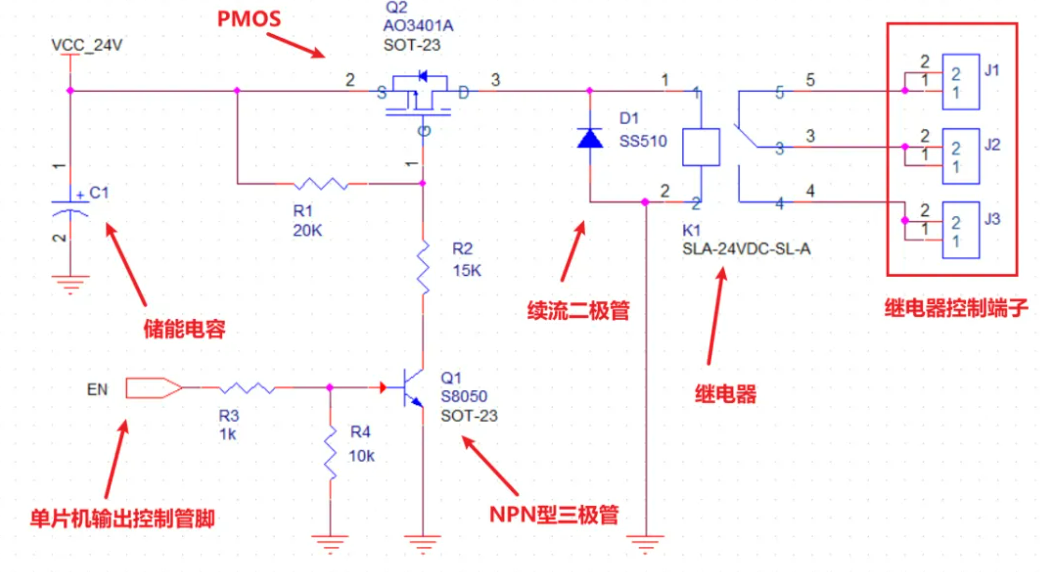

#嘉立创PCB#这是朋友讨论的问题,与以往的NMOS/NPN型三极管作为低端控制继电器不同的是,讨论的电路是一个 PMOS高端控制继电器的电路 。朋友问这个电路设计的有没有问题,电路图如下:

电路实现功能:

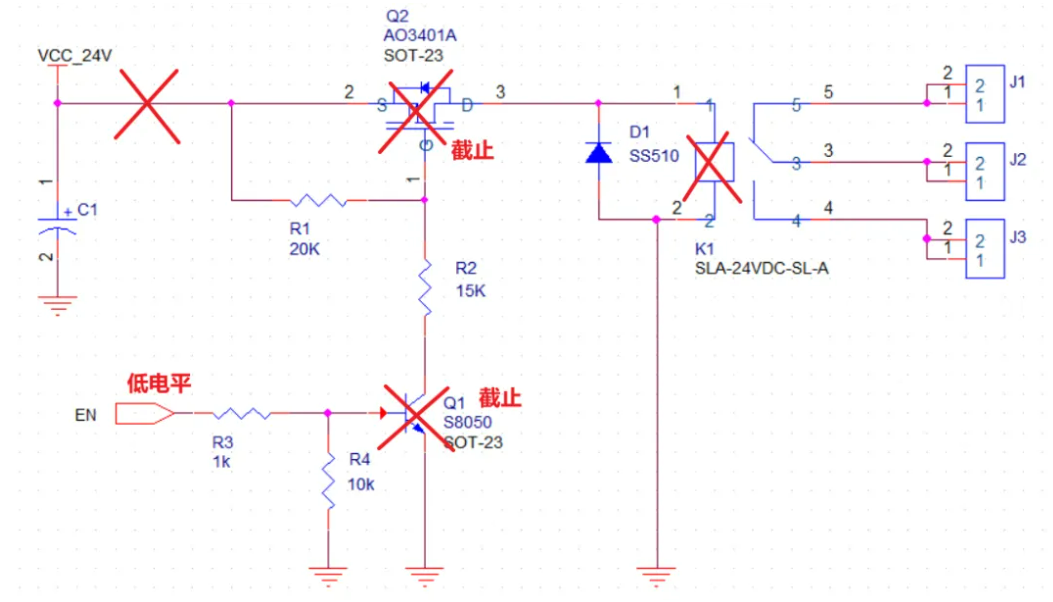

当EN为低电平时,三极管Q1截止,从而Vgs≈0V,PMOS管Q2截止,继电器不通电弹开。

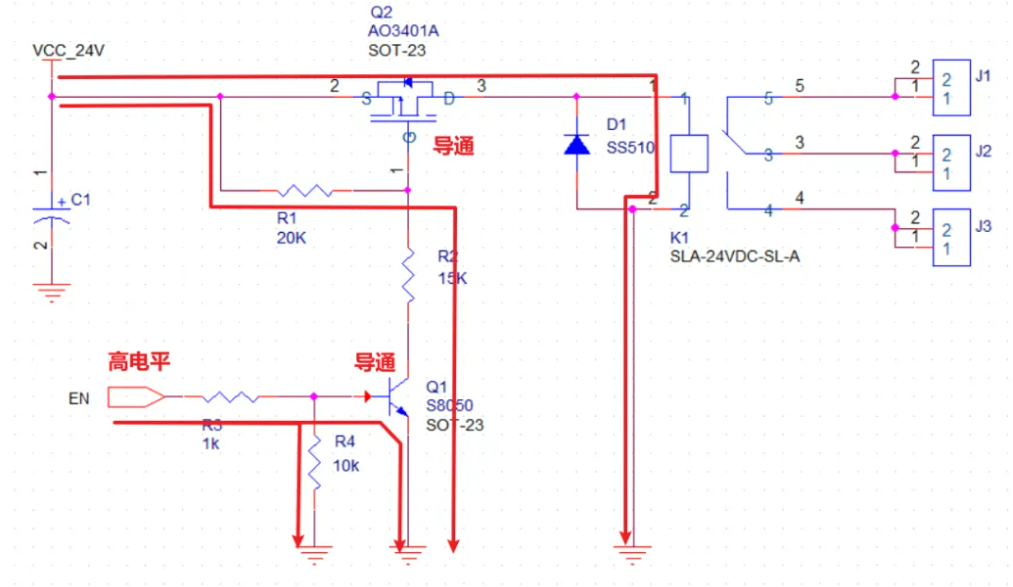

当 EN为高电平 时,三极管 Q1导通 饱和,Vce≈0.2V,从而Vg≈Vce+[(24-0.2)*15/35] = 10.2+0.2= 10.4V,那么Vgs ≈ 10.4-24 ≈-13.6V, 达到PMOS管Q2的导通电压 (万代 AO3401的最大导通值为-1.3V ),从而 Q2导通 , 继电器通电 吸合。电流路径如下图所示:

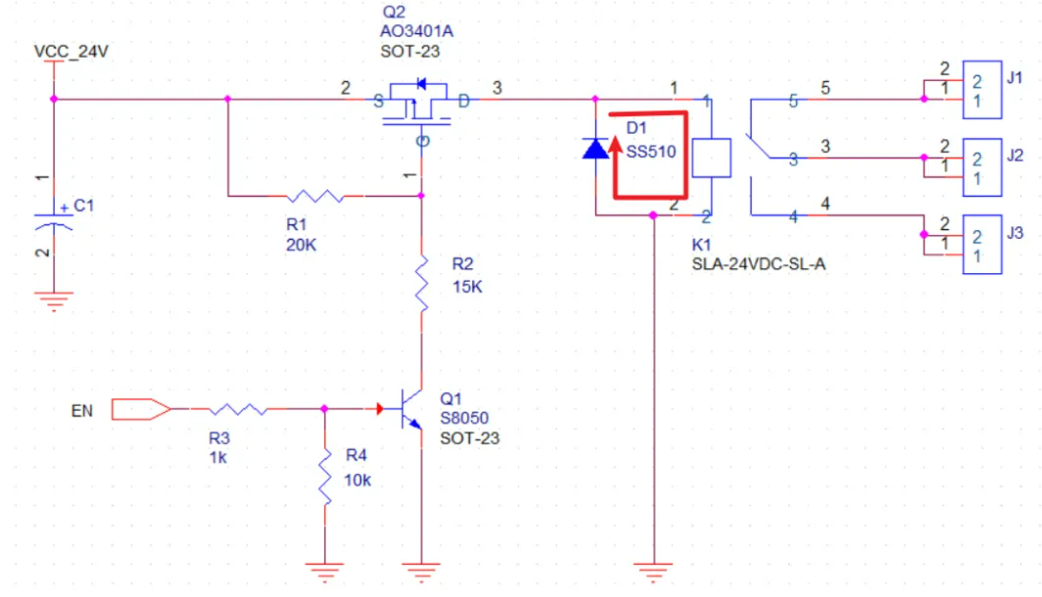

继电器从通电状态到断电状态,会有 续流二极管D1为继电器作续流。防止继电器产生的反向电压击穿Q2与Q1 。续流路径如下图所示:

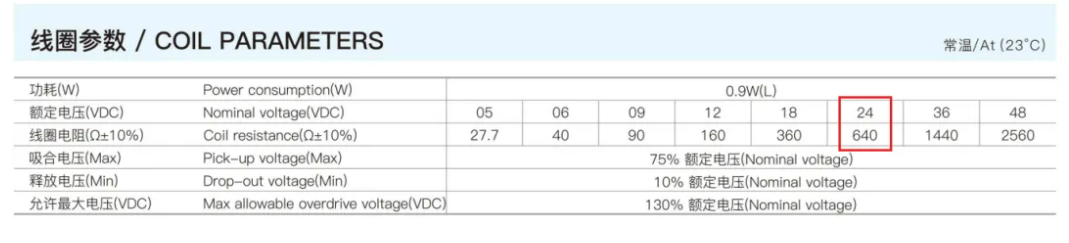

从继电器的规格书如下,可以看到电路符合继电器的设计要求:

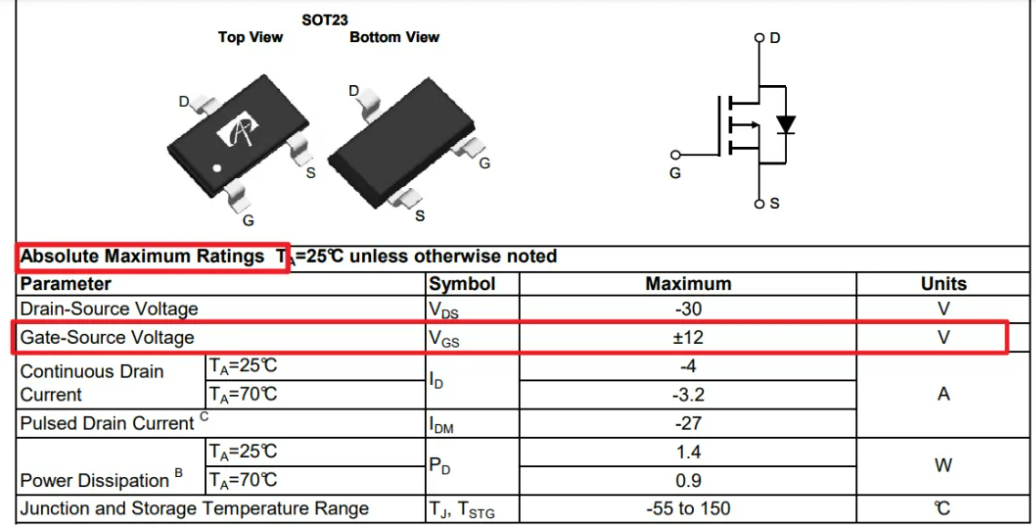

那么这个电路 有没有设计不合理的地方? 没错,就是一个 比较容易忽略的参数,那就是MOS管的Vgs ,打开MOS管AO3401的数据手册(以万代的手册为例),可以看到 AO3401的VGS的最大电压为±12V 。那么由刚刚的分析可知,Vgs稳态电压大概在-13.6V左右,而这个电压值大于了AO3401的Vgs最大值,这是很危险的:

所以最终的讨论结果为:将R1与R2的阻值互换,并且可以再适当减小R1的阻值,降低Vgs(这款继电器电流不是很大),以防电源有一些过压波动的情况会导致Vgs大于绝对最大值导致MOS管击穿损坏。

总结:设计电路时要格外注意Vgs是否存在过压,以防电路出现异常,过压情况MOS很容易击穿。

#嘉立创PCB#

#嘉立创PCB#

互动量:952

互动量:952

登录 或 注册 后才可以进行评论哦!