认证的核对指标,大体基于频谱参数

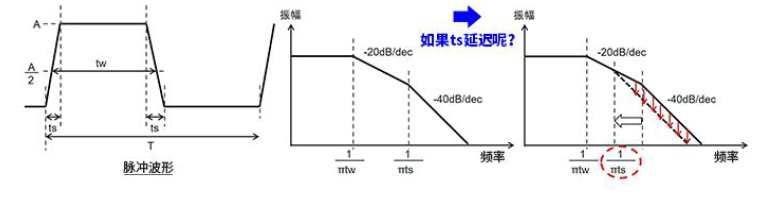

首先来看下面的原理示意图。

在表示开关信号的脉冲波形中,包括 tw(脉冲宽度)和 ts(上升/下降时间)。

中间的图是基于傅里叶变换的理论上的脉冲波形频谱。这是“振幅随着频率的升高而衰减,衰减斜率随着 tw 和 ts 而变化”的常见频谱。

右图表示脉冲的 ts 延迟后的频谱变化。斜率变为-40dB/dec 时的 1/πts 频率降低

是理所当然的,最终结果是其后的振幅减少。简而言之就是“当 ts 延迟时频谱的振幅

衰减”。

接下来将使用实际的频谱分析仪数据来看频率等其他参数变化时的频谱变化。这里的关键点是“对于信号波形的变化,频谱将以怎样的趋势变化”。这是用来通过实际的开关电源电路的开关相关的频谱来分析并解决 EMC问题所必须的知识。

* 波形变化与频谱变化

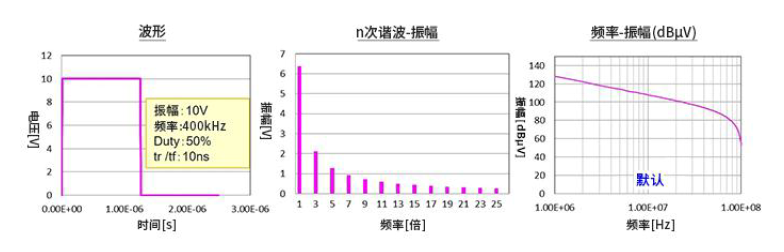

前面给出的图是用来比较的默认条件下的数据。下面波形图中的条件是:振幅 10V,频率 400kHz,Duty(占空比)50%,tr/tf(上升时间/下降时间)10ns。

中间的图表示 n 次谐波和振幅(V)的关系。1 倍的频率=基波,也就是说 400kHz的分量最大,以奇数倍的频率形成频谱。

谐波仅为奇数次是 Duty 为 50%=1:1 的频谱特征。各分量的大小为基波分量的 1/次数,例如 3 次谐波分量为 1/3,n次谐波分量为1/n。

右图是振幅为 dBµV 的对数曲线图。顺便提一下,dBμV 是基于以 1µV 电压为基准的电压比的 dB 值。

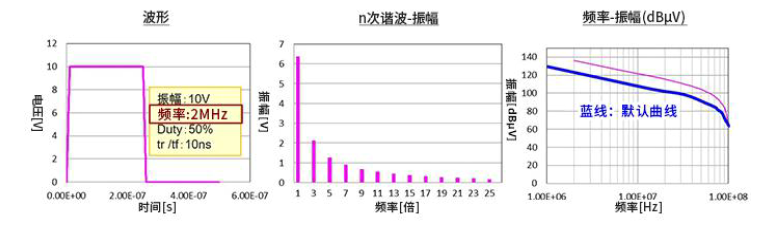

①将频率变更为 2MHz 时的频谱。从频率-振幅(dBµV)关系图可以明确看出,当频率增加时振幅整体增加。

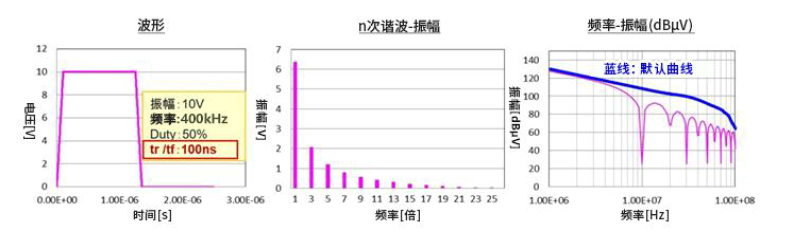

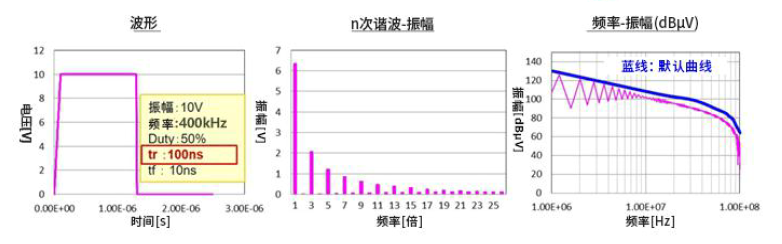

②tr 和 tf 同时延迟为 100ns 时的频谱。结果如原理示意图所示,进入-40dB/dec衰减时的频率降低,频谱的振幅衰减。

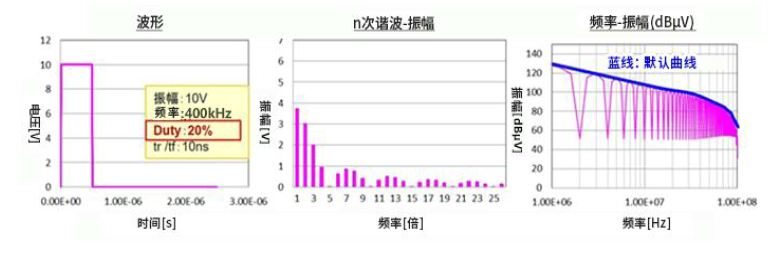

③将 Duty50%变为 20%时的频谱。由于 Duty 不是 1:1,因此会产生偶次谐波,但峰值基本上没变化。随着脉冲宽度 tw变窄,基波频谱的振幅衰减。

④仅 tr(上升时间)延迟时的频普。tr 相关的分量因 tr 延迟而从更低的频率开始衰减。

下面汇总了每种情况的结果。总而言之,当频率较低且上升/下降较慢时,频谱会衰减。从 EMC 的角度来看,也就是频谱的振幅较低时更有利。

二,认证过程中,输入端线材的长度会形成闭合环路,产生噪声,分为差模(常模)噪声与共模噪声

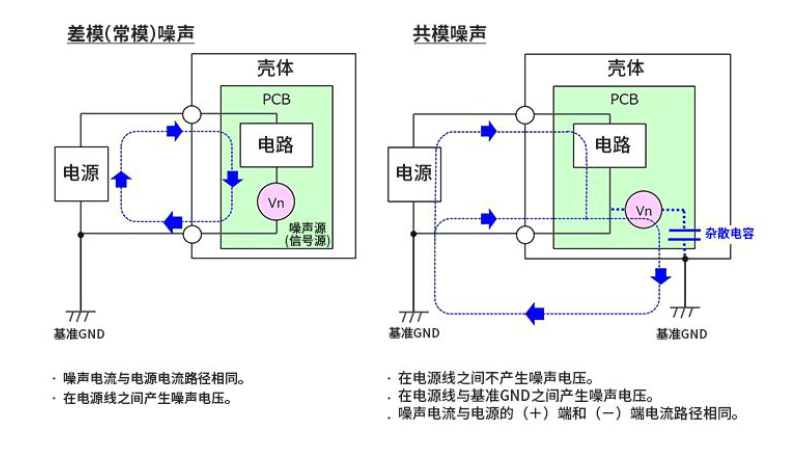

传导噪声可分为两种。一种是“差模噪声”,也称为“常模噪声”。这两种称呼有时可根据条件区分使用,不过在本文中作为相同的名词处理。另一种是“共模噪声”。

来看下图。本文是围绕电源展开介绍的,因此图例是将带有电路的印刷电路板(PCB)装在壳体中,并由外部给电的示例图。

差模噪声产生在电源线之间,是噪声源对于电源线串联进入,噪声电流与电源电流方向相同。由于往返方向相反而被称为“差模(Differential mode)”。

共模噪声是经杂散电容等泄漏的噪声电流经由大地返回电源线线的噪声。因电源的(+)端和(-)端流过的噪声电流方向相同而被称为“共模(Common mode)”。在电源线间不产生噪声电压。

如前所述,这些噪声即为传导噪声。不过,由于电源线中流动着噪声电流,因此会发出噪声。

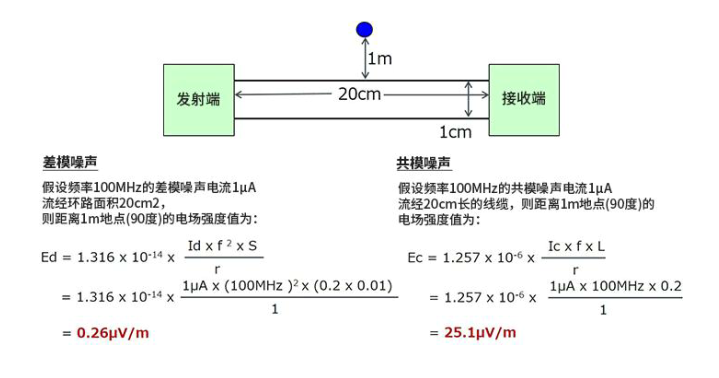

由差模噪声引起的辐射的电场强度 Ed 可通过左下方的公式来表示。Id 为差模中的噪声电流,r 为到观测点的距离,f 为噪声频率。差模噪声会产生噪声电流环,因此环路面积 S 是非常重要的因素。如图和公式所示,假设其他因素固定,环路面积越大则电场强度越高。

由共模噪声引起的辐射的电场强度 Ec 可通过右下方的公式来表示。如图和公式所示,线缆长度 L 是非常重要的因素。

为了更好地认识每种噪声引发的辐射特点,接下来代入实际数值来计算一下电场强度*1。条件完全相同。电场强度的观测点用蓝色圆点来表示。*1:公式来源-EMC工学详解 实用降噪技法

这个计算结果中非常重要的一点是:噪声电流值相同的情况下,共模噪声辐射要大得多(在本例中约大 100 倍)。不管怎样,这些传导噪声和辐射噪声即 EMI 如果超出了容许范围,就需要采取降噪对策。特别需要记住的是,在考虑辐射噪声对策时,针对共

模噪声的对策是非常重要的。

关于具体对策,后续会逐步介绍,其中最原则性的噪声对策是差模噪声要减少环路面积 S(比如线缆采用绞合线),共模噪声要极力缩短线缆长度。不过一定会遇到受配置和材料等限制的情况,此时需要探讨增加滤波器的方法。

三,开关电源产生的噪声

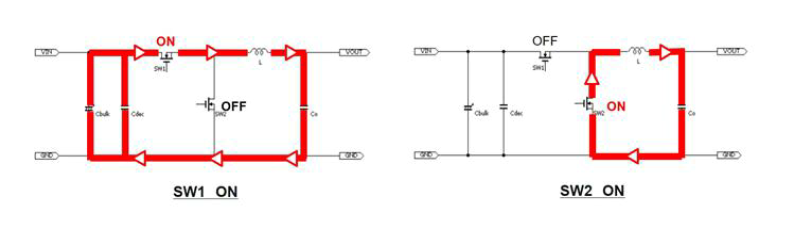

首先,使用同步整流型降压 DC/DC 转换器的等效电路来了解一下开关电流的路径。

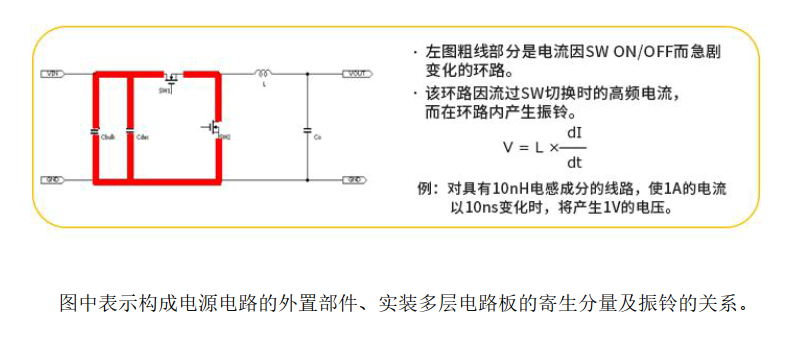

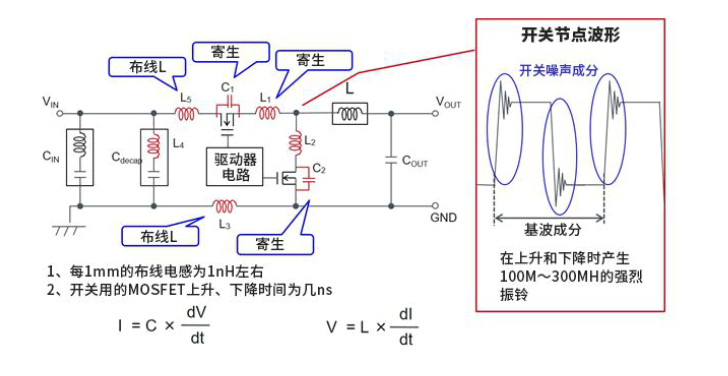

SW1 为高边开关,SW2 为低边开关。SW1 导通(SW2为OFF)时,电流路径是从输入电容器到 SW1、再经由电感 L 到输出电容器。SW2 导通(SW1 为 OFF)时,电流路径是从SW2 经由 L 再到输出电容器。下图表示这些电流路径的差分,每当开关ON/OFF时,红色线路的电流都会急剧变化。该环路的电流变化非常剧烈,所以会因 PCB 板布线电感而在环路内会产生高频振铃。

红色部分标出的是上图所表示的电流在急剧变化的环路中的寄生分量。布线中存在布线电感,通常每 1mm 有 1nH 左右的电感。另外,电容器中存在等效串联电感 ESL,MOSFET的各引脚间存在寄生电容。因此,如红框内的图例所示,开关节点将产生 100MHz~300MHz的振铃。所产生的电流及电压,可通过两个公式求得。

此振铃会作为高频开关噪声带来各种影响。虽然有采取相应的措施,但由于无法从电源 IC 处去除安装电路板的寄生分量,因此只能通过 PCB 板布局设计及采用去藕电容来解决。关于 PCB 板布局,在 DC/DC 转换器的“PCB板布局”部分有详细介绍,请参考。

* 噪声对策步骤

如前所述,盲目的对策只会增加损失。在确定对策之前,需要遵循以下几个步骤:

步骤 1:把握开关波形的频率成分

需要确认开关频率、上升/下降、过冲/下冲、振铃等与基波同时产生的不同现象的频率成分。这有助于根据希望解决的目标噪声的频率来确定不同的对策方法和相应部件,如果选择不当,效果则可能不理想。

步骤 2:把握噪声产生源与传导路径确认所产生的开关噪声是从哪一路径传导到一次侧或二次侧的。噪声对策需要在噪声的传导路径实施。而且,必须对所有的传导路径采取对策。哪怕忽略了一处传导路径,对策也是不完全的。

步骤 3:强化 GND

噪声对策的最后一步是增加降噪部件,但在此之前应该先探讨加强 PCB(印刷电路板)的 GND。优异的 GND 设计不仅可降低噪声,还是提升性能和稳定性的重要环节。通过强化 GND,可降低环路的阻抗。另外,还可有效提升滤波器的效果。

步骤 4:增加滤波器等降噪部件

最后是根据噪声的种类和性质,探讨相应的噪声对策部件并在电路中添加相应部件,比如通过滤波器来滤除、通过旁路电容来旁路滤除、通过芯片磁珠等的电阻成分来吸收噪声等。滤波器、旁路电容的效果等如步骤 3 所述,会受GND好坏的影响,所以请务必先强化 GND。

差模滤波器采用电容器、电感、铁氧体磁珠和电阻等。图例中是使用了 LC 的π型滤波器。各部件对噪声具有如下作用:

电容器:将噪声电流旁路到 GND。

电感:反射噪声电流。

铁氧体磁珠:将噪声电流的低频信号通过电感成分反射、高频信号通过电阻成分转换为热。

电阻:将噪声电流转换为热。

共模滤波器对于共模噪声的对策是使用共模滤波器(共模扼流圈)。共模滤波器大致可以分电源线路用和信号线路用两种。在开关电源的输入端一般使用电源线路用的共模滤波器,通过提高共模电流路径的阻抗来切断路径。

****使用电容器降低噪声

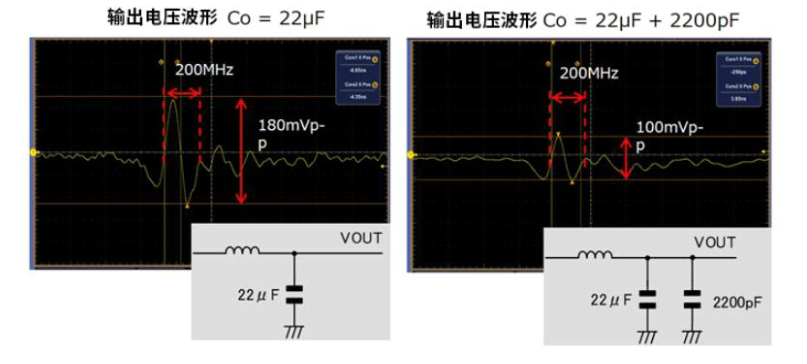

使用电容器降低噪声的示意图,下面是通过添加电容器来降低 DC/DC 转换器输出电压噪声的示例。

左侧的波形是输出端 LC 滤波器的电容为 22µF 时,在约 200MHz 的频率范围存在180mVp-p 左右的噪声(振铃、反射)。右侧波形是为了降低这种噪声而添加了 2200pF电容后的结果。从波形图可以看出,添加 2200pF 的电容使噪声降低了100mV左右。

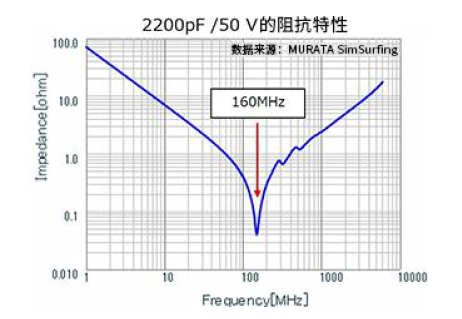

这里应该思考的是“为什么是 2200pF”。下图为所添加电容器的阻抗频率特性。

之所以选择 2200pF 的电容,是因为阻抗在 160MHz附近最低,利用这种阻抗特性,可降低噪声幅度约 2MHz。

这是通过添加电容器来降低目标噪声频率的阻抗,从而降低噪声幅度的手法。

像这样通过添加电容器来降低噪声时,需要把握噪声(振铃、反射)的频率,并选择具有相应阻抗的频率特性的电容器。

要点

1.通过降低目标噪声频率的阻抗来降低噪声幅度。

2.降噪用电容器的选型需要根据阻抗的频率特性进行(而非容值)。

***LC滤波器降低噪声

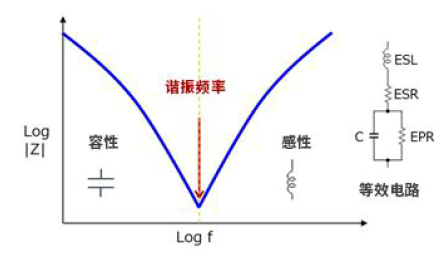

探讨利用电容器来降低噪声时,充分了解电容器的特性是非常重要的。下图为电容器的阻抗和频率之间的关系示意图,是电容器最基础的特性之一。

电容器中不仅存在电容量 C,还存在电阻分量 ESR(等效串联电阻)、电感分量 ESL(等效串联电感)、与电容并联存在的 EPR(等效并联电阻)。EPR 与电极间的绝缘电阻 IR 或电极间有漏电流的具有相同的意义。可能一般多使用“IR”。

C 和 ESL 形成串联谐振电路,电容器的阻抗原则上呈上图所示的 V 字型频率特性。

到谐振频率之前呈容性特性,阻抗下降。谐振频率的阻抗取决于 ESR。过了谐振频率之

后,阻抗特性变为感性,阻抗随着频率升高而升高。感性阻抗特性取决于ESL。

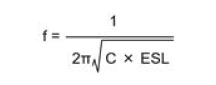

谐振频率可通过以下公式计算:

从该公式可以看出,容值越小、ESL 越低的电容器,谐振频率越高。如果将其应用于噪声消除,则容值越小、ESL 越低的电容器,频率越高,阻抗越低,因此可以很好地消除高频噪声。

虽然这里说明的顺序有些前后颠倒,不过使用电容器降低噪声的方法,是利用了电容器“交流通过时频率越高越容易通过”这个基本特性,将不需要的噪声(交流分量)经由信号、电源线旁路到 GND 等。

下图为不同容值的电容器的阻抗频率特性。在容性区域,容值越大,阻抗越低。另外,容值越小,谐振频率越高,在感性区域阻抗越低。

下面总结一下电容器阻抗的频率特性:

1. 容值和 ESL 越小,谐振频率越高,高频区域的阻抗越低。

2. 容值越大,容性区域的阻抗越低。

3. ESR 越小,谐振频率的阻抗越低。

4. ESL 越小,感性区域的阻抗越低。

****去耦电容降低噪声

去耦电容有效使用方法的要点大致可以分为以下两种。另外,还有其他几点需要注意。本文就以下三点中的“要点 1”进行介绍。

要点 1:使用多个去耦电容

要点 2:降低电容的 ESL(等效串联电感)

其他注意事项

使用多个去耦电容

去耦电容的有效使用方法之一是用多个(而非 1 个)电容进行去耦。使用多个电容时,使用相同容值的电容时和交织使用不同容值的电容时,效果是不同的。

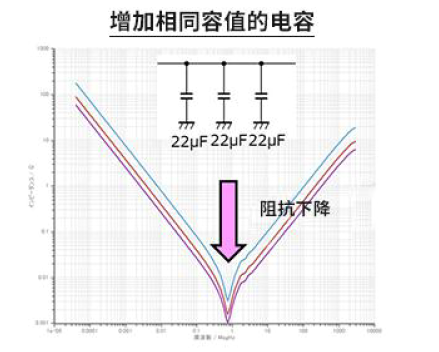

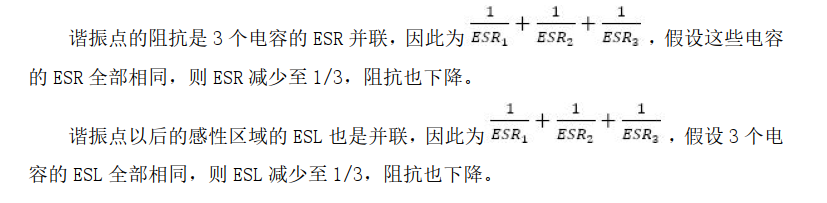

1.使用多个容值相同的电容时

下图是使用 1 个 22µF 的电容时(蓝色)、增加 1 个变为2个时(红色)、再增加 1个变为 3 个(紫色)时的频率特性。

如图所示,当增加容值相同的电容后,阻抗在整个频率范围均向低的方向转变,也就是说阻抗越来越低。

这一点可通过思考并联连接容值相同的电容时,到谐振点的容性特性、取决于 ESR(等效串联电阻)的谐振点阻抗、谐振点以后的 ESL(等效串联电感)影响的感性特性来理解。

并联的电容容值是相加的,所以3 个电容为 66µF,容性区域的阻抗下降。

由此可知,通过使用多个相同容值的电容,可在整个频率范围降低阻抗,因此可进一步降低噪声。

2.使用多个容值不同的电容时

这些曲线是在 22µF 的电容基础上并联增加0.1µF、以及 0.01µF 的电容后的频率特性

通过增加容值更小的电容,可降低高频段的阻抗。相对于一个 22µF 电容的频率特性来说,0.1µF 和 0.01µF 的特性是合成后的特性(红色虚线)。

这里必须注意的是,有些频率点产生反谐振,阻抗反而增高,EMI 恶化。反谐振发

生于容性特性和感性特性的交叉点。

所增加电容的电容量,一般需要根据目标降噪频率进行选型。

另外,在这里给出的频率特性波形图是理想的波形图,并未考虑 PCB 板的布局布线

等引起的寄生分量。在实际的噪声方法中,需要考虑寄生分量的影响。

要点:

1.去耦电容的有效使用方法有两个要点:①使用多个电容,②降低电容的ESL。

2.使用多个电容时,容值相同时和不同时的效果不同。

*****调整电感降低噪声

首先,电感(线圈)具有以下基本特性,称之为“电感的感性电抗”

①直流基本上直接流过。

②对于交流,起到类似电阻的作用。

③频率越高越难通过。

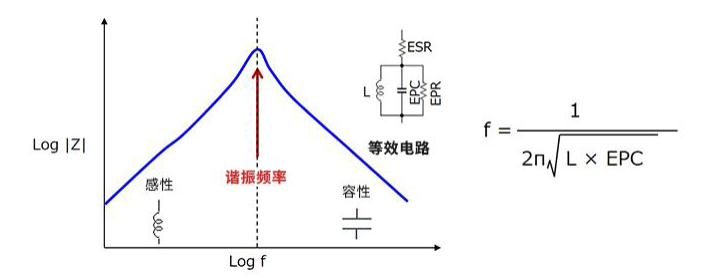

下面是表示电感的频率和阻抗特性的示意图。

在理想电感器中,阻抗随着频率的提高而呈线性增加,但在实际的电感器中,如等效电路所示,并联存在寄生电容 EPC,因而会产生自谐振现象。

所以,到谐振频率之前呈现电感本来的感性特性(阻抗随着频率升高而增加),但谐振频率之后寄生电容的影响占主导地位,呈现出容性特性(阻抗随着频率升高而减小)。也就是说,在比谐振频率高的频率范围,不发挥作为电感的作用。

电感的谐振频率可通过上述公式求得。除了主体是电容量还是电感量的区别外,该公式与电容的谐振频率公式基本相同。从公式中可以看出,电感值 L 变小时谐振频率会升高。

电感的寄生分量中,除了寄生电容 EPC 之外,还有电感绕组的电阻分量 ESR(等效

串联电阻)、与电容并联存在的 EPR(等效并联电阻)。电阻分量会限制谐振点的阻抗。

要点:

1.电感在谐振频率之前呈现感性特性(阻抗随频率升高而增加)。

2.电感在谐振频率之后呈现容性特性(阻抗随频率升高而减小)。

3.在比谐振频率高的频段,电感不发挥作为电感的作用。

4.电感值 L 变小时,电感的谐振频率会升高。

5.电感的谐振点阻抗受寄生电阻分量的限制。

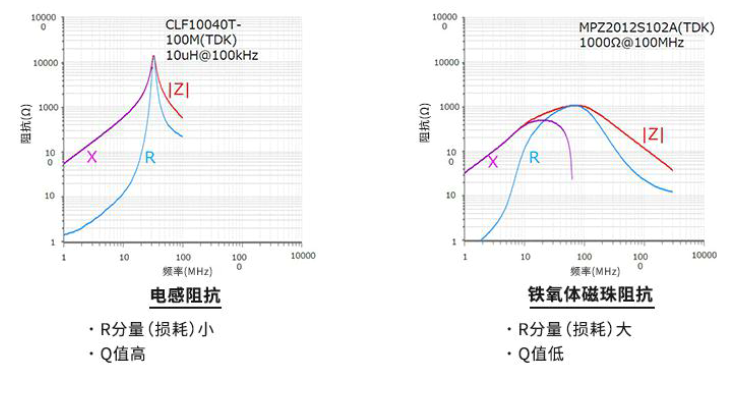

使用电感和铁氧体磁珠降低噪声的方法

仅使用电容无法充分消除噪声时,可以考虑使用电感。降噪方法中使用的电感大致

有两种。

①绕组型电感:构成滤波器,

②铁氧体磁珠:将噪声转换为热。

铁氧体磁珠与普通电感相比,具有电阻分量 R 较大、Q 值较低的特性。利用该特性可消除噪声。

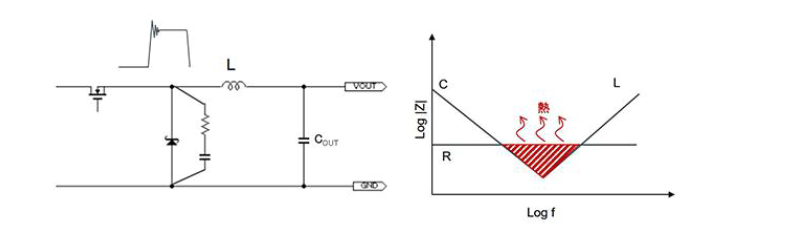

***SW端增加EMC吸收电路去降低噪声

RC 缓冲电路

为了降低开关节点产生的尖峰电压,可考虑增加 RC 缓冲电路。在下面的示例中,整流二极管关断(高边开关导通)时,RC 缓冲电路可将二极管的接合部、寄生电感、寄生电容、PCB 版图的电感中积蓄的电荷放电,并通过电阻转换为热,从而降低尖峰电压。

RC 的值一般以 R=2Ω、C=470pF左右为出发点,通过实际确认来找出最佳值。

需要注意的是,增加缓冲电路会导致开关转换变慢,效率下降,所以需要探讨噪声

水平和效率之间的平衡点。

另外,前提是电阻将噪声电压转换为热,所以需要注意电阻的容许损耗。电阻的损

耗可通过以下公式计算出来:

损耗=C×VIN2×fSW

缓冲电路不仅可用于低边侧,在高边侧也经常使用。

要点:

1.RC 缓冲电路可通过电阻将寄生电容、寄生电感等产生的尖峰电压转换为热,从而

降低尖峰电压。

2.增加缓冲电路可能会导致效率降低,因此需要探讨噪声水平和效率之间的平衡点。

3.电阻是将噪声电压转换为热,因此需要注意电阻的容许损耗。

****通过重新布局电路板,排查串扰进行降低噪声

这个不做解释,遵循LAYOUT准则即可,

有不了解,没吃透的欢迎联系本人 QQ 1173726120

\n#电路设计与技巧# #电路设计与技巧#

#电路设计与技巧#

互动量:204

互动量:204

登录 或 注册 后才可以进行评论哦!

还没有评论,抢个沙发!