相信大家对该通信的大部分基础理论知识已经了然如胸了,在开发过程中使用SPI通信问题应该不会太大,但SPI作为一种嵌入式工程师们如此青睐的通信方式,在开发中总会有人挖一些坑让你来填,当然这个人可能是自己。

在定位这些问题的时候动不动就几天过去了,项目工程师又要来催了~

那么今天bug菌根据以往的经验,将重点从通信的速度、容错性和结构这三个方面进一步谈谈SPI通信,也算是完结篇了。

1、通信速度

对于SPI通信并没有规范最高的通信速率,在我的开发经验中有见过达到50Mbit/s的应用场景,但通常比较常见的还是10Mbit/s左右。

具体选用多快的通信速度,还得在实际项目中根据情况具体设计,比如:

1、当前主从机的主频和项目的具体应用都与SPI数据的处理能力有着直接关系,一般SPI通信的时钟频率都是来源于主频分频,这就在一定程度上限制了其通信速率上限。

即使能够达到较高速的速率,而处理器还需要处理更多的业务逻辑,再去处理SPI数据也是不够及时的,此时高速率并没有太大的意义了。

2、SPI硬件PCB布线长度等等影响着线路阻抗,这也同样限制了通信速率,一般通信距离越长,通信速度越低,否则容易造成通信不稳定。

特别是通信线路经过一些干扰源更是影响其稳定性,所以SPI作为一种相对高速的通信方式,一般都不会用于长距离通信中,而是大量用于微处理器与外部SPI接口的设备之间的通信,比如高速采样芯片ADC、处理器之间等等。

3、前面说了即使SPI主机能够达到较高的通信速率,但从机主频或者数据处理能力不够,这样也是没有太大意义的,当你可以通过配置从机为接收队列或者DMA等方式进行优化,当然高速率在多机中能够减少同步延时。

值得注意的是一些芯片标称的最高通信速率,是在比较好的外界条件下的测试值,超过了该标称值可能也能用,但并不会很稳定,容易导致通信异常。

所以具体选用多快的通信速度,还需根据实际情况分析确认。

2、容错性

SPI不像IIC那样存在应答机制,也没有流控制机制,当从机配置较低,如果一个报文还没处理完,后一个报文又到来,导致传输错乱,其通信过程几乎都是靠硬件来保证数据的传输稳定性,是一种不可靠传输。

当然如果是用于多机通信倒是可以通过制定可靠性校验协议来保证传输数据的稳定,但这也在一定程度上会降低通信的有效数据传输速度。

像stm32的SPI外设发送和接收都存在独立的CRC校验功能,大致的原理就是使用CRC在每个位上进行串行计算,然后在最后一次数据传输结束时来传输CRC校验值,接受方接收到CRC以后自动拿着数据和CRC值进行比对,看是与否有数据故障,如果存在传输问题就会置位相应的CRC故障标志位告知。

当然如果所选用的芯片SPI外设没有独立CRC模块可以模拟类似的操作进行处理,只是相对比较耗时,毕竟这个CRC得软件自己处理。

stm32的SPI外设的灵活度远不止这些,比如配置成双线单向模式等,可以把MISO和MOSI都向一个方向传输,从而提高一倍的传输速度,感兴趣可以参考一下手册玩一下。

3、通信模式

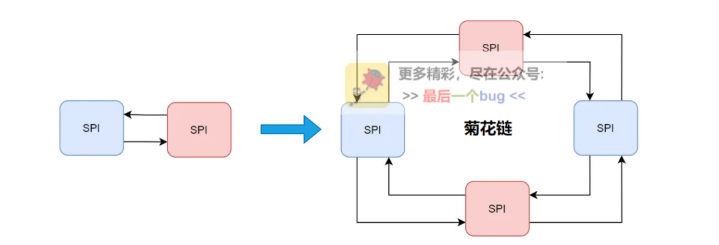

SPI通信拓扑结构上的一大特色就是菊花链拓扑。

上篇文章跟大家介绍的SPI一主多从的通信方式属于并行方式,要控制多个从机需要使用大量的GPIO信号来控制片选信号。

似乎非常简约的SPI通信一下子变得不那么简单了,特别是布线方面是非常低效的,此时菊花链的通信方式便有了一席之地。

菊花链模式下的SPI所有的片选和串联时钟信号都可以共用一条线,其数据以时钟节拍逐个bit的循环移动,从而完成数据传递,这样就大大减少了控制线路。

当凡事总有其两面性,采用链式结构相对并联方式没有那么灵活,主机无法一次任意选中一个从机进行直接通信,而是得通过数据的循环传递。

另外对于链式结构主从关系没有那么直接,相连接的从机之间存在着更多的依赖关系,一旦链路或者从机出现了问题,其影响是联锁的。

菊花链的通信方式应用是非常多的,比如当我们在一块板上有多块控制芯片,但此时由于PCB大小的限制,可以选用菊花链的拓扑方式实现一个JTAG仿真器对多个JTAG芯片进行烧录和控制。

互动量:643

互动量:643

登录 或 注册 后才可以进行评论哦!

还没有评论,抢个沙发!