高速外部无源晶振(HEXT)抗干扰设计

描述如何提高芯片使用外部无源晶体振荡电路的稳定性和抗干扰能力,特别针对强干扰环境给出有效解决措施,避免微控制器时钟源不稳引发故障。

1 概述

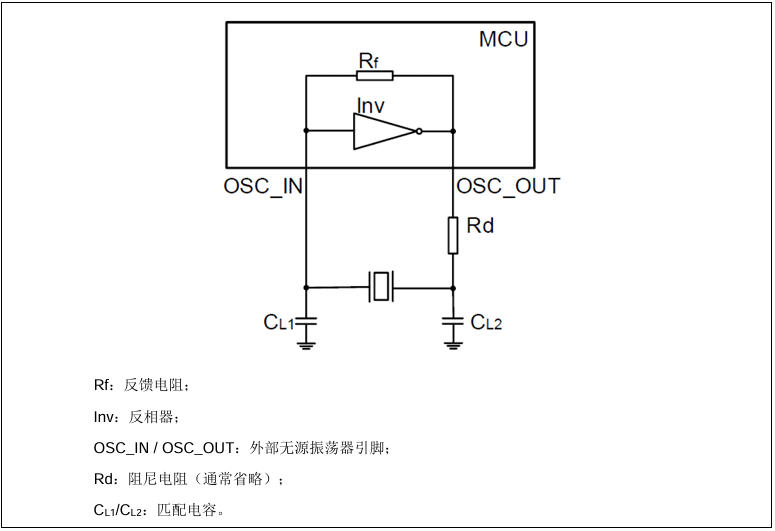

稳定的时钟源是微控制器系统中一切逻辑电路的基础。微控制器高速主时钟源若采用外部无源振荡器(HEXT),产生的时钟信号可以实现时钟稳定性、准确性和硬件成本的平衡。AT32系列微控制器高速外部时钟源可以使用无源振荡器与内部起振电路构成皮尔斯(Pierce)振荡电路,架构如图1所示。

图 1. 皮尔斯振荡电路架构图

皮尔斯振荡电路是正弦波振荡电路的一种,通过引入正反馈和选频网路实现稳定的自激振荡。在电路中,反馈的实现是通过反馈电阻Rf将反相器的输入和输出相连接,使反相器工作在线性放大区域,以提供稳定振荡所需增益;选频网络通过振荡器的并联谐振频率选择特性以实现放大器对特定频率信号的放大。

皮尔斯振荡电路属于全模拟电路,其抗干扰能力较弱,在外部强干扰的环境下,标称MHz等级的晶体振荡频率可能会因注入干扰能量,进入异常工作状态,而产生几百兆赫兹的异常高频频率。被干扰形成的高频时钟信号进入微控制器内部再经过PLL的倍频,会使微控制器系统运行时钟远超规格,从而造成复位、代码跑飞、或死机等故障。这种想要在强干扰的情况下,又要保持稳定振荡频率的应用需求,需要特别加以注意,在外部振荡电路设计时要额外加以处置。

如图2所示范例,当用5 W对讲机靠近晶振电路时,若振荡电路未特别加以处置,一般很容易造成系统运作异常。此时根据雅特力的测试经验,一个8 MHz晶振的频率当干扰出现时会产生高达445 MHz的异常高频;而25 MHz晶振可以产生的异常高频到954 MHz。异常高频频率与对讲机频率并不存在对应关系,可能与不同晶振晶体的自身特性相关。

图 2. 用 5 W 对讲机干扰高速外部晶振电路

2 通用设计规则

一般情况下,雅特力微控制器若没有因使用 OTGHS 功能、OTGFS 主机模式、或 CAN(CANFD)功能而必需使用 HEXT 为系统时钟来源时,推荐使用内部 HICK 为时钟源。因为 HICK 为内部振荡时钟,为芯片内部信号,因此有强大的抗干扰能力;另外也提供全温度范围最大不超过 2.5 %的频率准确特性,大部分的应用条件都可正常使用。因此若没有其它特殊考量,HICK 适合大多数应用。

若是使用者有用到上述几个对时钟有要求的外设,或对时钟精准度和抖动程度有所要求,就一定得使用 HEXT 外挂晶体振荡器作为系统时钟来源。不过此时若晶体所处环境没有强的干扰源,高速无源晶振电路设计一般遵循以下通用设计规则,就能够取得良好的稳定性和足够的抗干扰能力。

晶振

※ 选择满足系统要求的最小频率晶振。

※ 晶体到微控制器两根时钟引脚(HEXT_IN 和 HEXT_OUT)之间的走线应尽可能短,远离其它高速器件和数字电路。

※ 尽可能保证两根走线的长度一致,因为不同长度引入的杂散电容不同,导致谐振器两个匹配电容取值时不相等;走线避免换层,以减小线路寄生电感。

※ 建议将晶振外壳接地,提高抗干扰能力。

※ 尽量选择 ESR 值小的晶体,通常封装越小的晶体其 ESR 越大。ESR 大的晶体起振时间会相对更长,抗干扰能力更弱。负载电容

※ 晶体的匹配电容目的是为调整振荡时钟频率的精度,一般都必需使用合适的负载电容;推荐使用温度系数较小的陶瓷电容(C0G/NP0)。

※ 负载电容尽量靠近 HEXT_IN 和 HEXT_OUT 引脚。

※ 在选择匹配电容时要考虑 PCB 板和微控制器引脚的杂散电容,可以通过微调匹配电容来调整频率。如果实测振荡频率过大则将匹配电容调大,如果实测振荡频率过小则将匹配电容调小,如此反复调节最终达到合适的频率。

PCB 设计

※ 整个振荡电路的走线和器件可以使用接地环进行包裹保护;振荡电路的器件摆放在同一层。

※ 不要在晶振电路附近或横跨电路底层走任何信号线(地线除外)。

※ 晶振属敏感器件,应当远离 PCB 边沿。

其它

※ AT32 系列微控制器内部振荡电路集成了反馈电阻 Rf,通常不需要外接反馈电阻即可实现正常起振,如果出现不起振的情况可以尝试在外部并联反馈电阻,通常取值为 1 MΩ 以上。

※ 部分 AT32 微控制器产品中提供了内部驱动能力调节功能,通过配置相应寄存器可以选择不同等级的驱动能力。请注意驱动能力的提升需符合晶体的规格要求。

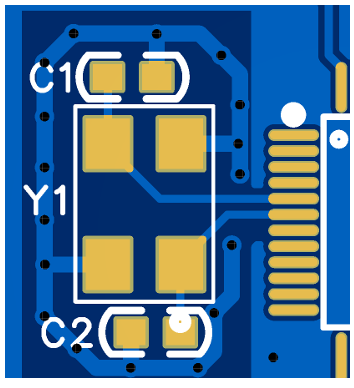

图 3. 高速外部无源晶振一般 layout 示例

3 抗强干扰设计措施

但对于一些特殊产品,其系统必须集成强干扰源,如大功率射频模块、和无线传输系统,或是使用环境中必定存在强干扰源时,就必须额外注意。雅特力根据实测和实际经验累积,在面对以上特殊的应用环境时,强烈建议使用者采取以下措施,以保证微控制器外部高速时钟源的稳定性,并最大程度加强其抗干扰能力。

屏蔽

为晶体和微控制器添加屏蔽罩,形成法拉第笼,防止电磁干扰;若微控制器因其它原因不能使用屏蔽罩,至少要保证晶体和HEXT_IN和HEXT_OUT走线置于屏蔽罩内。

PCB设计

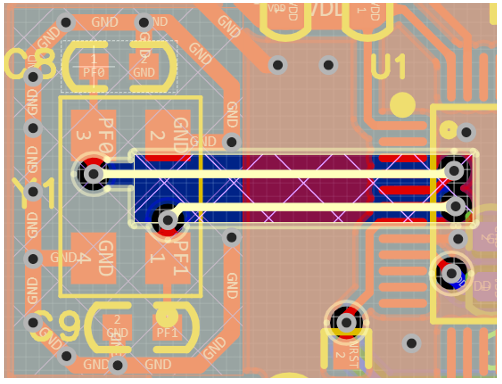

使用4层及以上PCB设计,将HEXT_IN和HEXT_OUT信号线走内层;外界干扰信号一般是通过耦合到HEXT_IN和HEXT_OUT信号线,再进入振荡电路被进一步放大。将HEXT_IN和HEXT_OUT信号线走内层类似于屏蔽的效果,防止干扰能量的侵入。

图 4. HEXT_IN 和 HEXT_OUT 信号走内层示例

磁珠

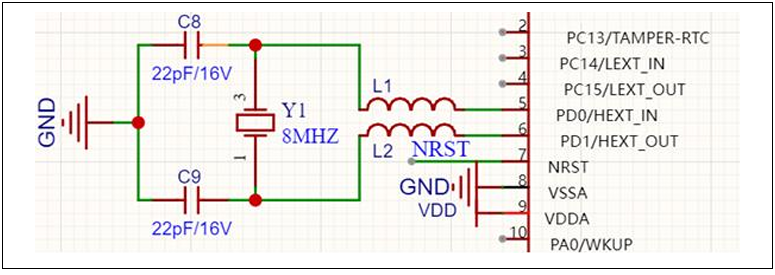

HEXT_IN和HEXT_OUT信号线串磁珠。磁珠对一般正常晶体振荡频率无影响,可视为直通通过;但它对于高频干扰信号具有抑制作用,将干扰能量以热能耗散,阻止干扰信号进入振荡电路。同时也因其高频高阻抗特性,可以打断干扰信号引起整个振荡电路形成异常高频的回路。需要注意的是,选择磁珠时要参考其阻抗频率曲线,不能影响到正常振荡频率,推荐使用470 Ω@100 MHz磁珠使用。图5之中L1和L2即为磁珠放置位置。

图 5. HEXT_IN 和 HEXT_OUT 信号串磁珠示例

互动量:19

互动量:19

登录 或 注册 后才可以进行评论哦!