--ST DDR应用文档

国际版 bing 英文搜索 DDR Application Note

Guidelines for DDR memory routing on STM32MP2 MPUs - Application note

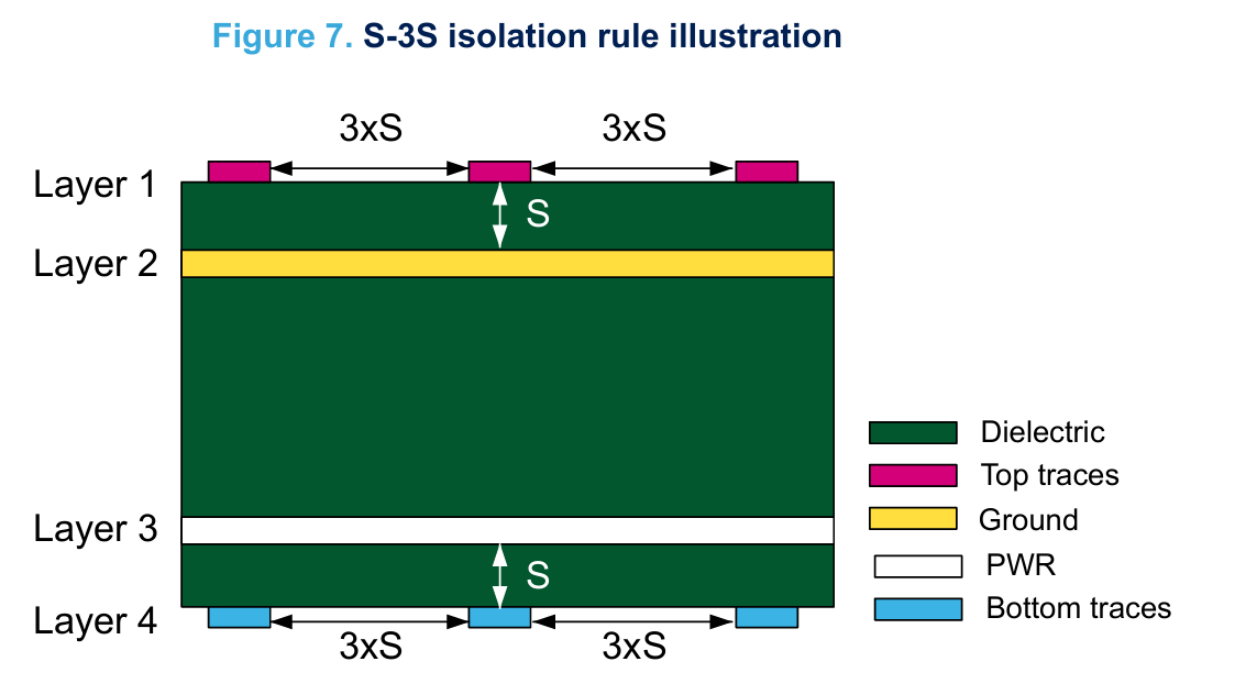

叠层推荐 S-3

走线紧挨着 完整参考层, 并且 参考层之间相邻s

目的:减少层间串扰

手段: S-3 S为参考面,当层间距离大于3倍S 走线间隔离

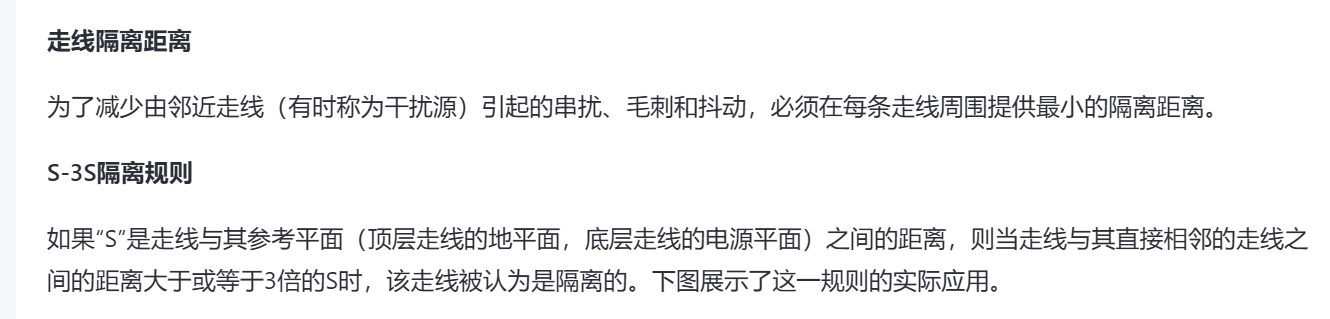

等长处理

常规的 蛇形走线 并非最优解

折返走线!

并且要考虑 封装内走线长度

STMicroelectronics提供的模板和长度均衡表格可以简化信号走线长度均衡的任务。这些表格包含了封装的走线长度,并可以在STMicroelectronics网站上找到,例如STM32MP2 MPU上的DDR内存布线示例,网址为 www.st.com。

STM32MP2 MPU上的DDR内存布线示例

差分信号不一定全是要等长

1可能引入额外延迟

2 对内的 不要登场,但是任何差分间距始终一致

3有效长度计算公式

关于组间和组内差分

问题来了,哪些差分要等长哪些否之?

------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

组内必须等长

组间 不必等长

------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

阻抗控制

单端 55ohm

差分100ohms

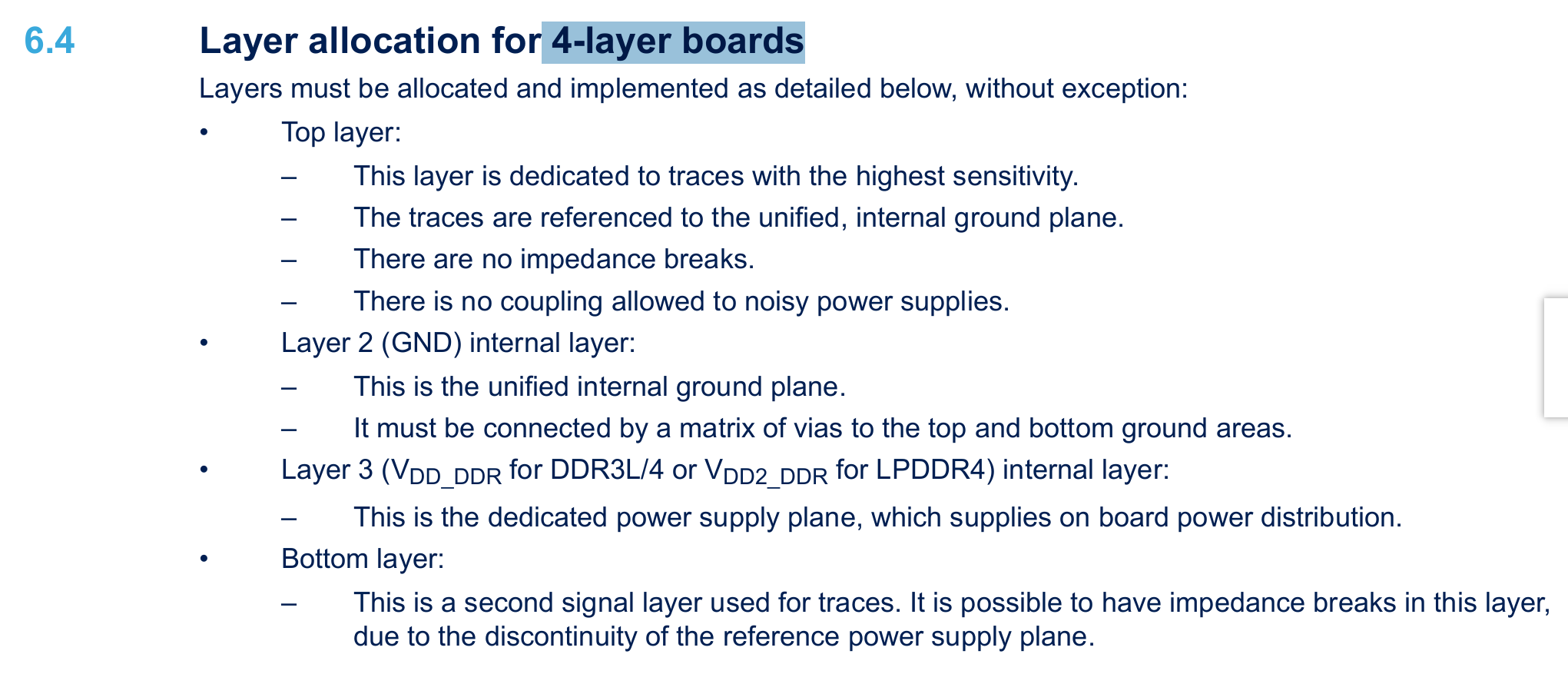

ST给出的叠层设计

4层板

- 01 SIG TOP-Layer 高敏感走线,有统一参考面,无阻抗不连续,无干扰电源耦合

- 02 GND 完整,打孔连接

- 03 POWER 专用电源,分配电源

- 04 SIG BOTTOM-LAYER 可能出现阻抗不连续(因为参考层可能不连续, 电源层可能划分割 ,不管有没有电压,只要电势稳定即可参考)

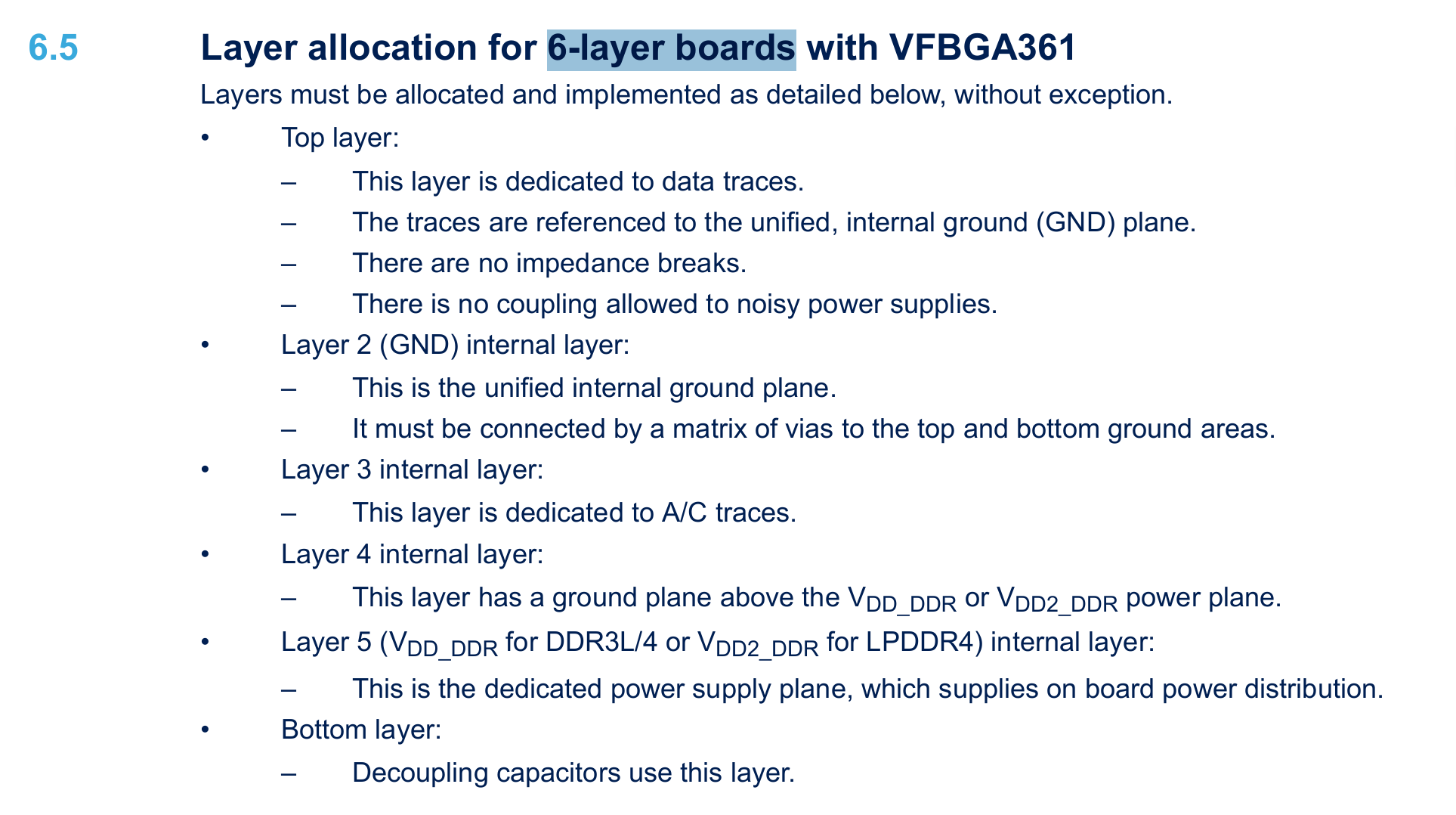

6层板

- 01 SIG -TOP-Layer

- 02 GND

- 03 SIG- 模拟线、控制线 ,注意隔离

- 04 GND-额外屏蔽

- 05 POWER

- 06 SIG - 去耦电容

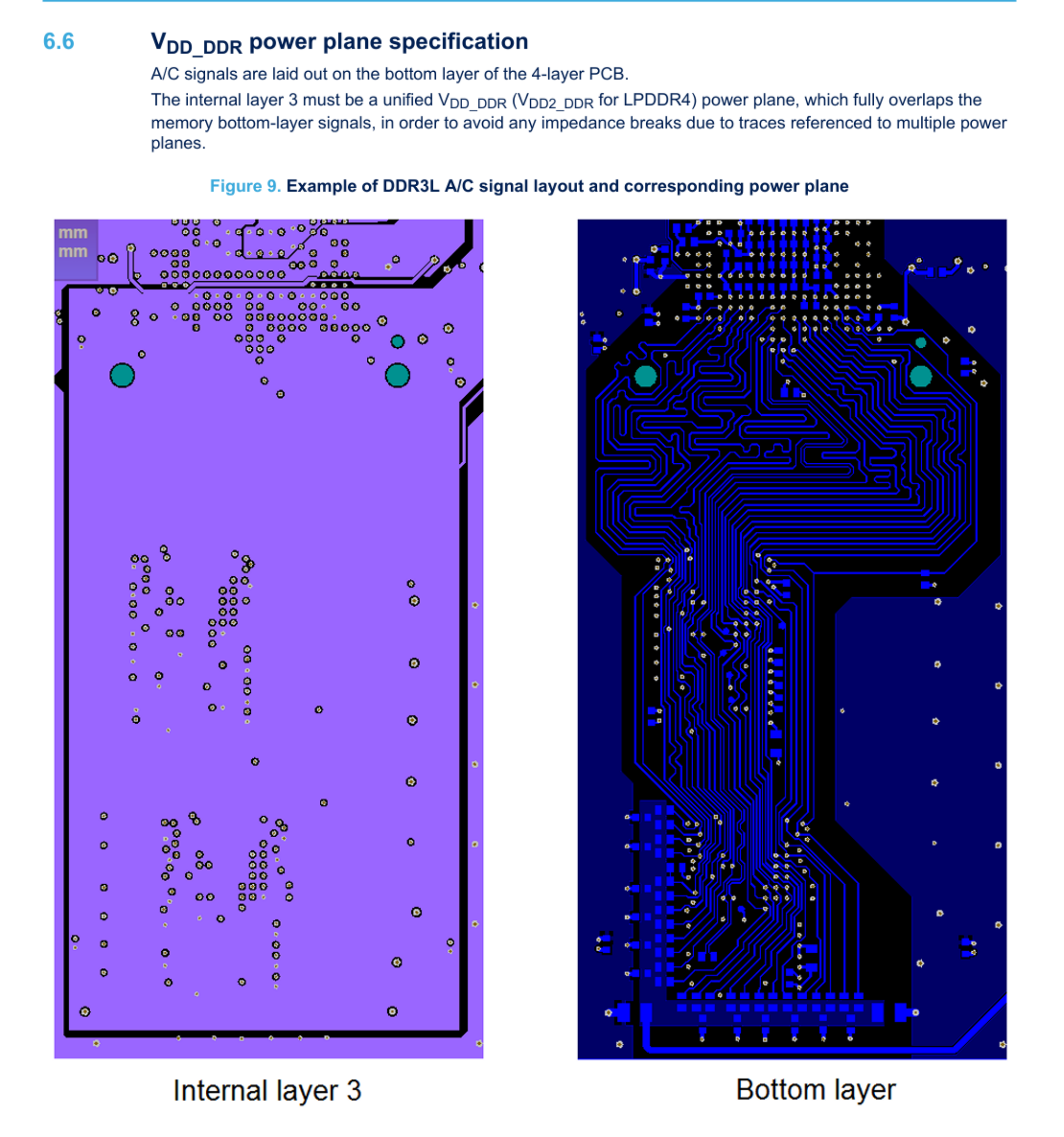

DDR内存布线示例

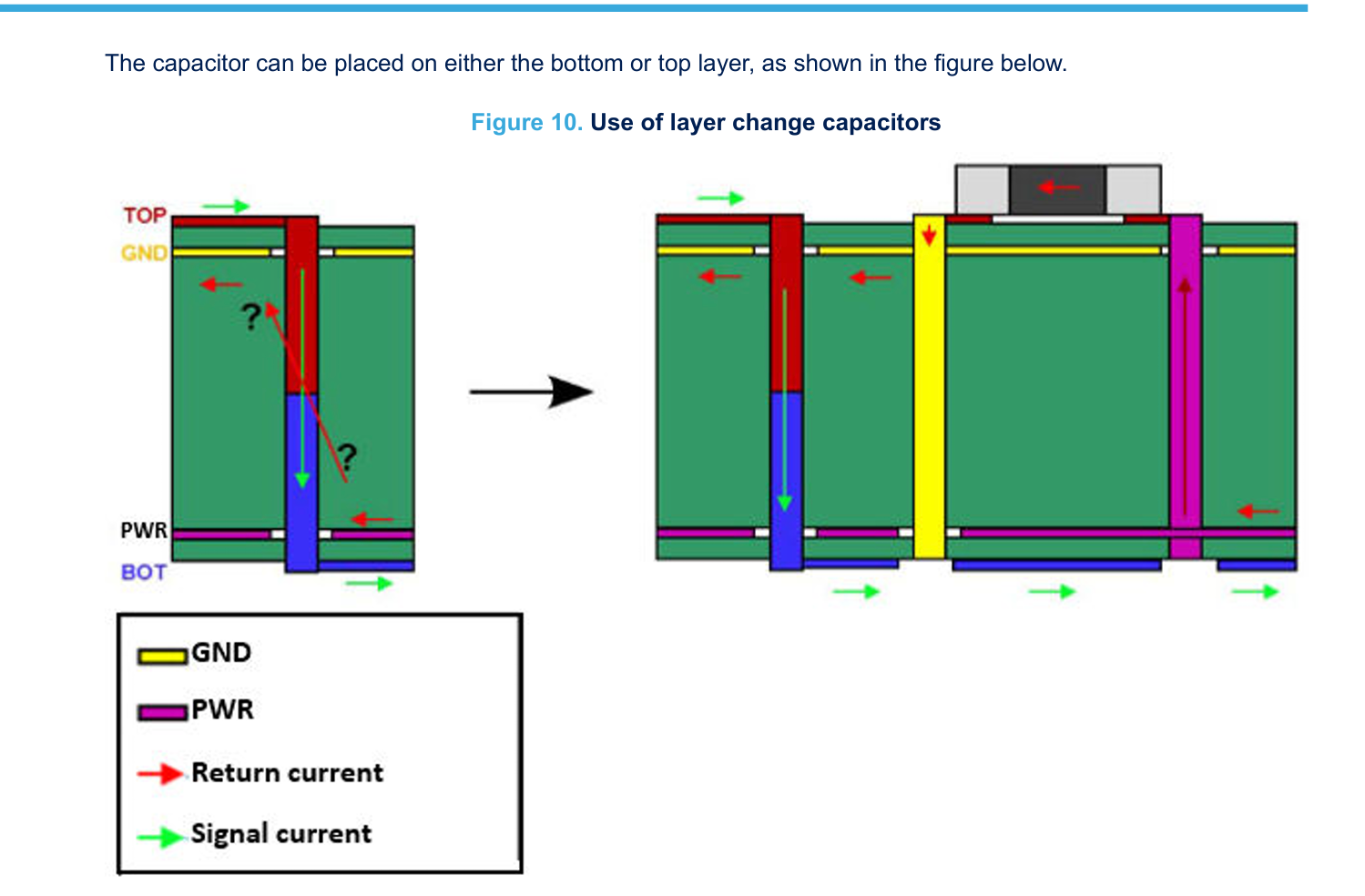

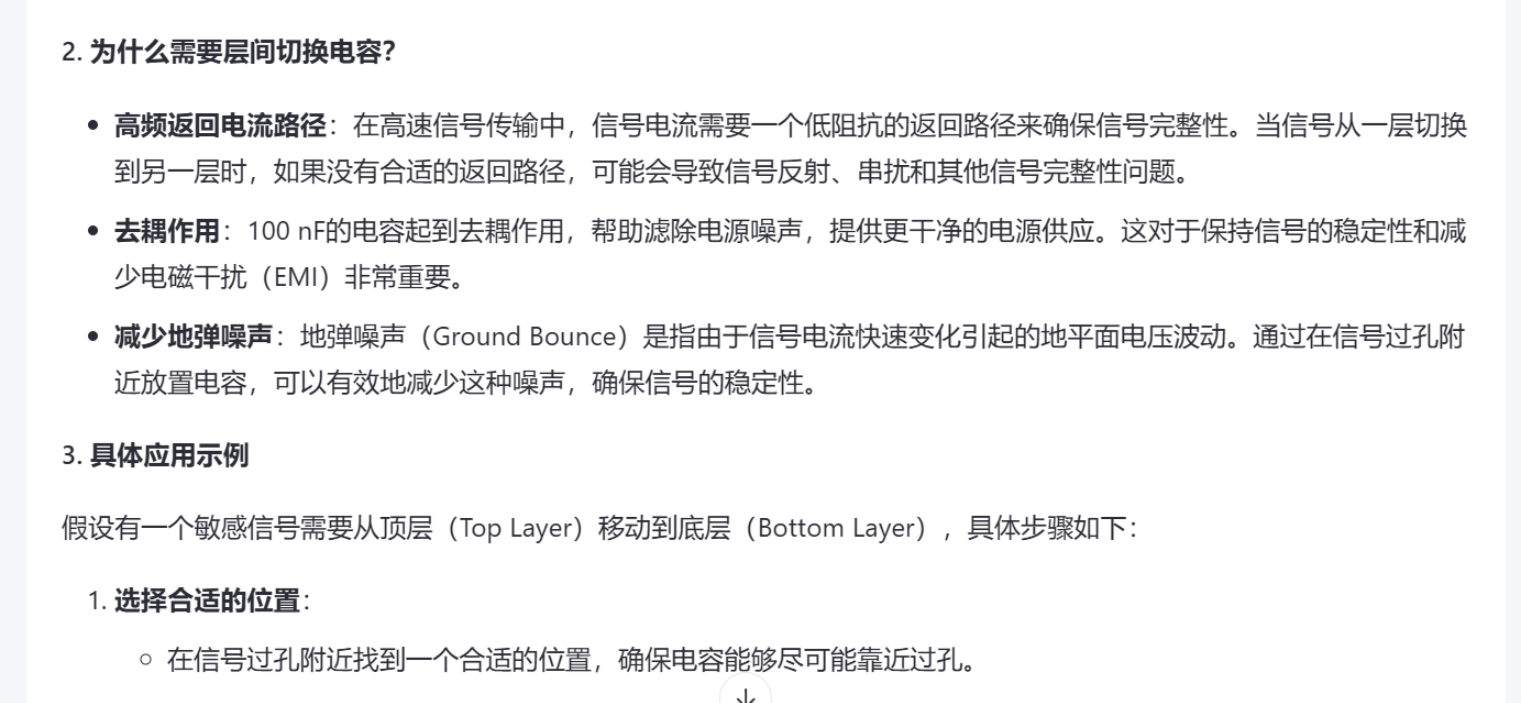

切换电容

什么是切换电容,如何用

为什么用

可以一组过控放置一个切换(层)电容

更高频率干扰,可以放更小的 切换电容,减少走线,避免额外寄生电感

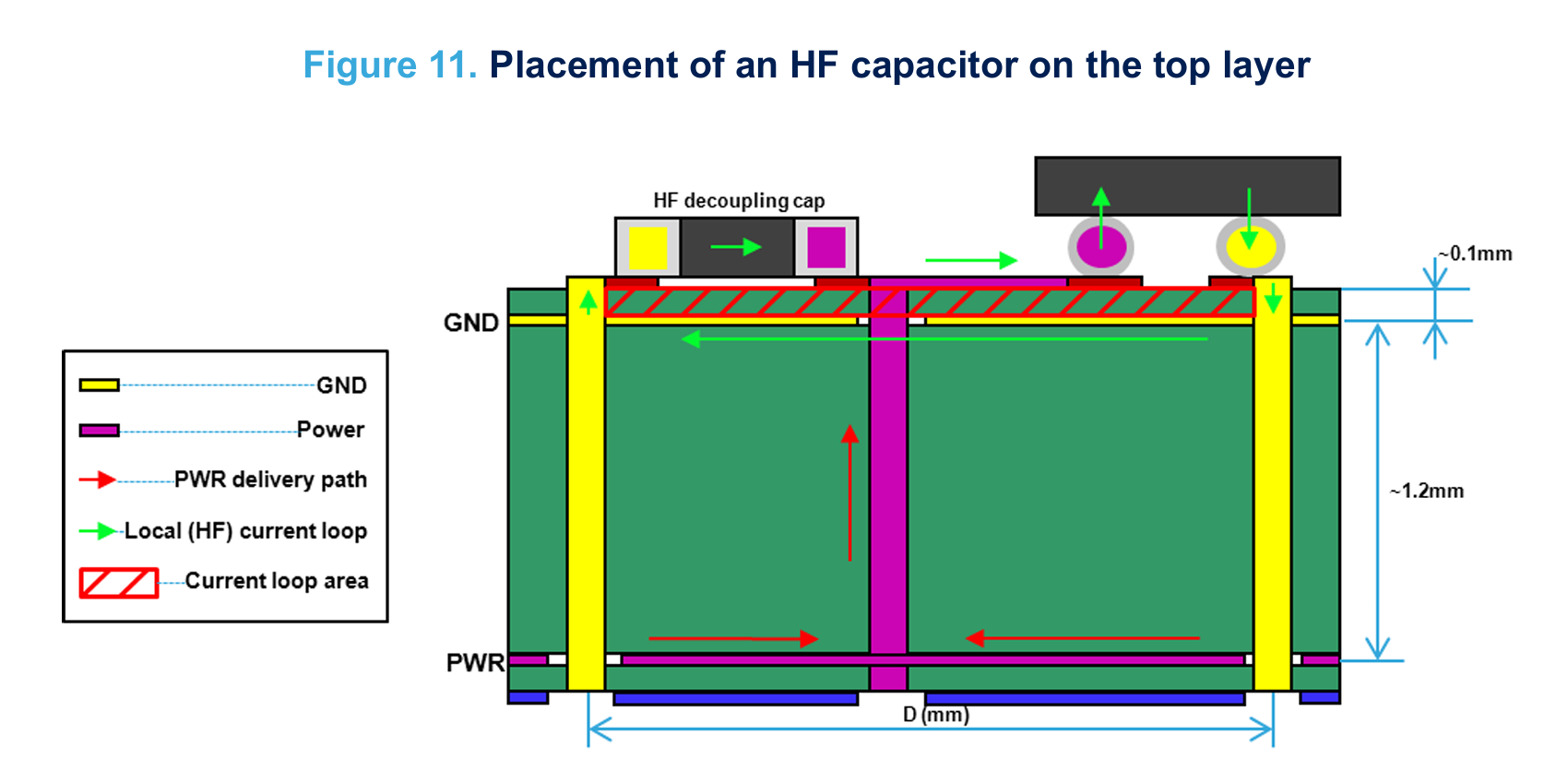

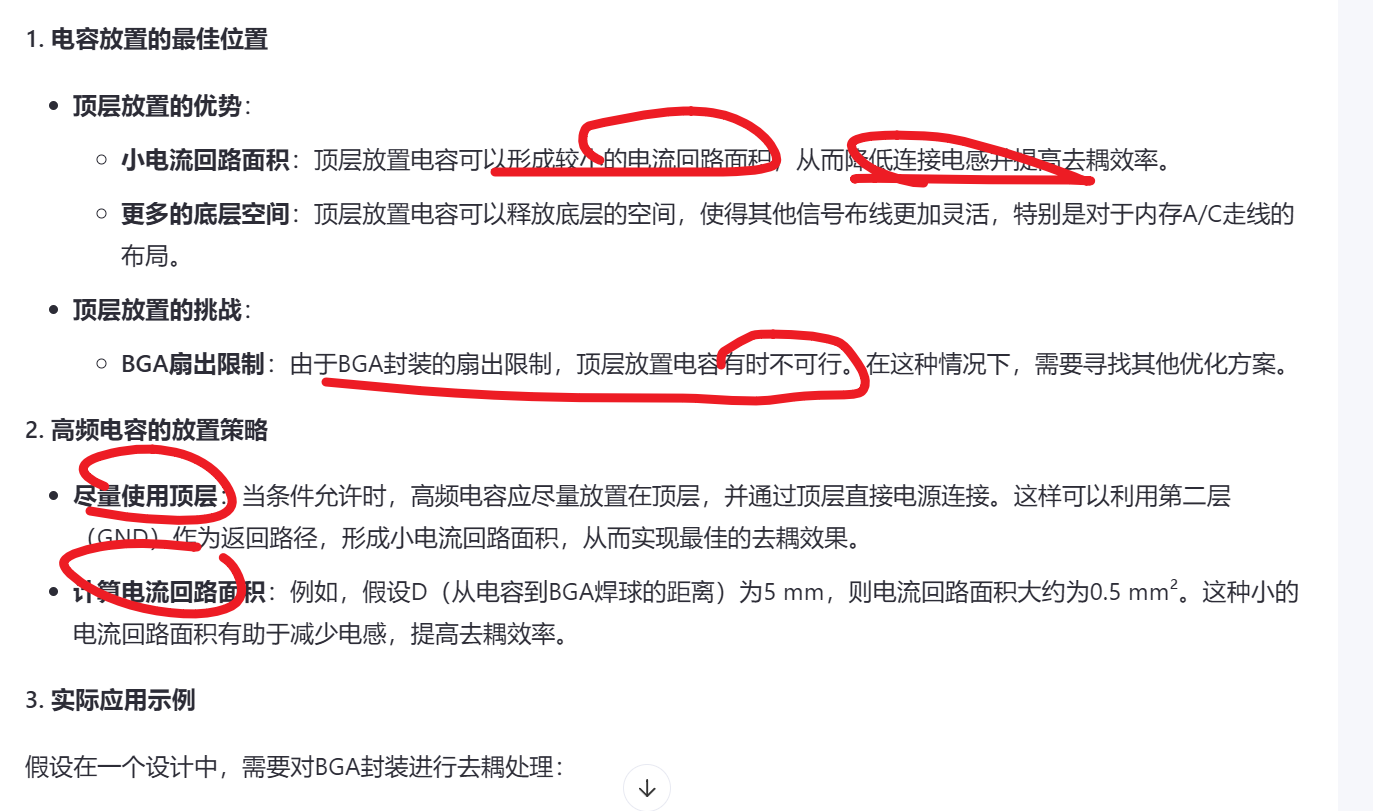

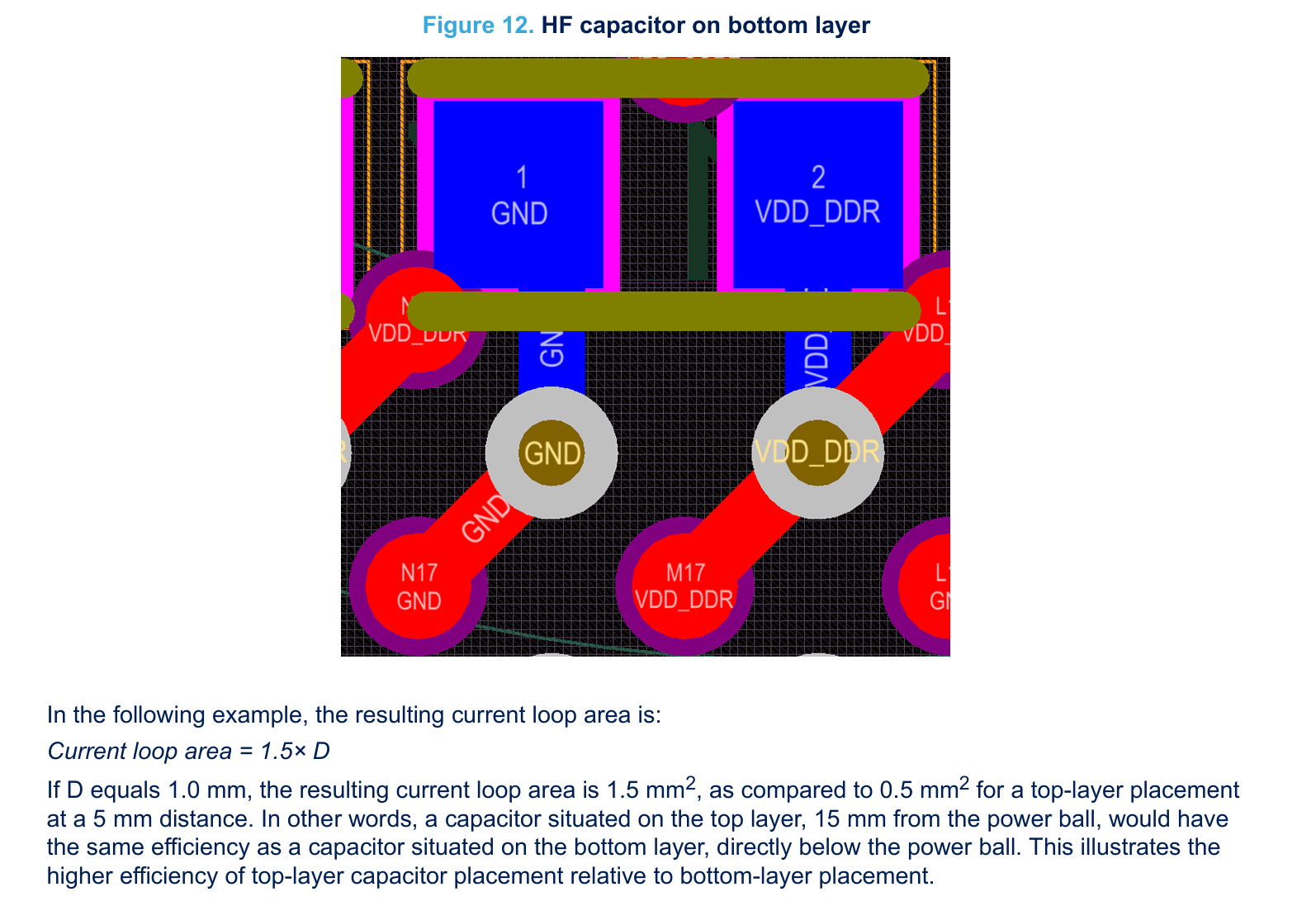

高频电容 布局

顶层 效果大于底层效果

能放顶层就放顶层

去耦效果更好

放在BGA芯片底部 回流线时

回流面积会影响 寄生电感的大小

红色阴影区为 回流区

回流面积计算

说明为什么 放在顶层更好, D在图片中显示,也许是电容走线距离

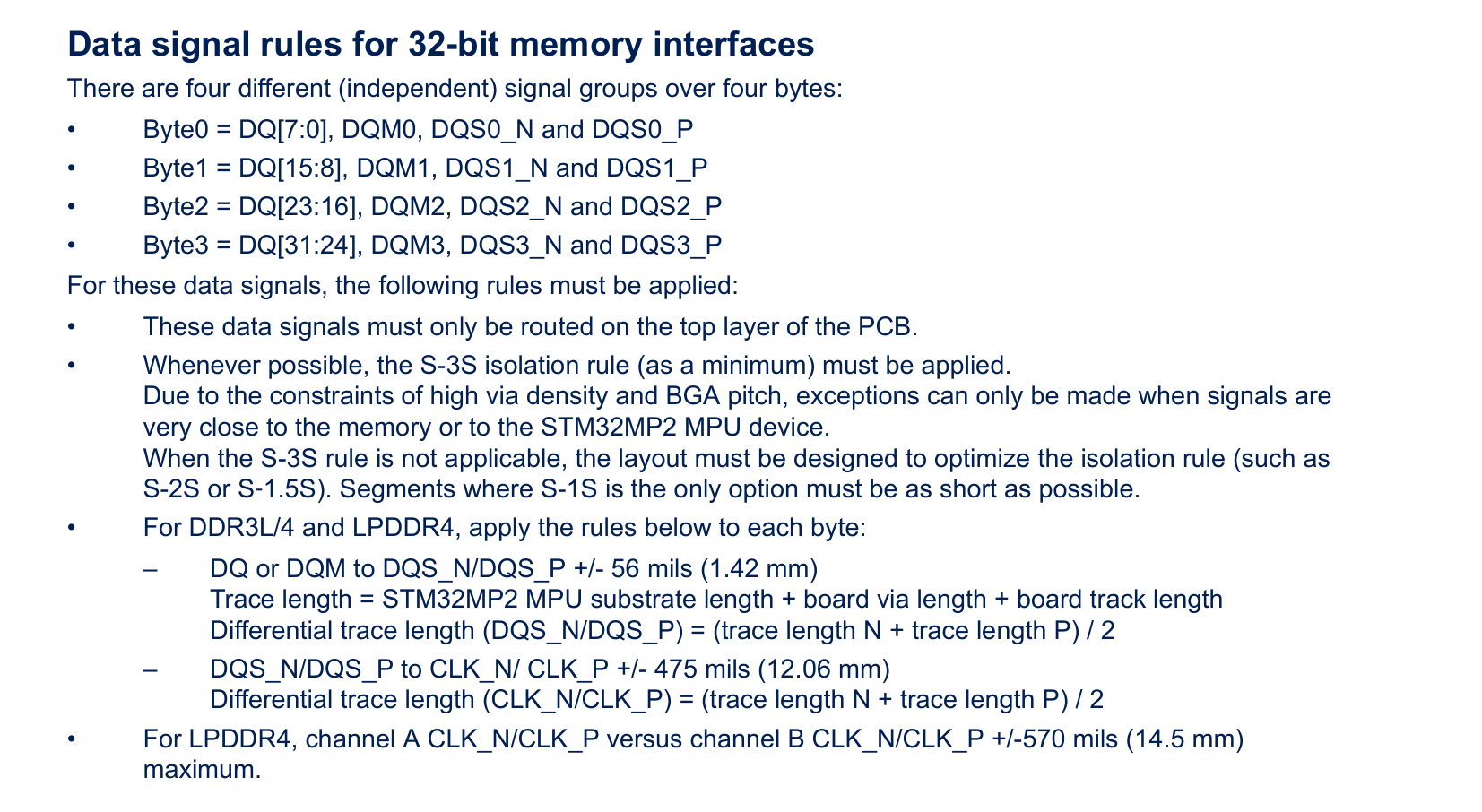

DDR的数据线分组定义

先说了定义

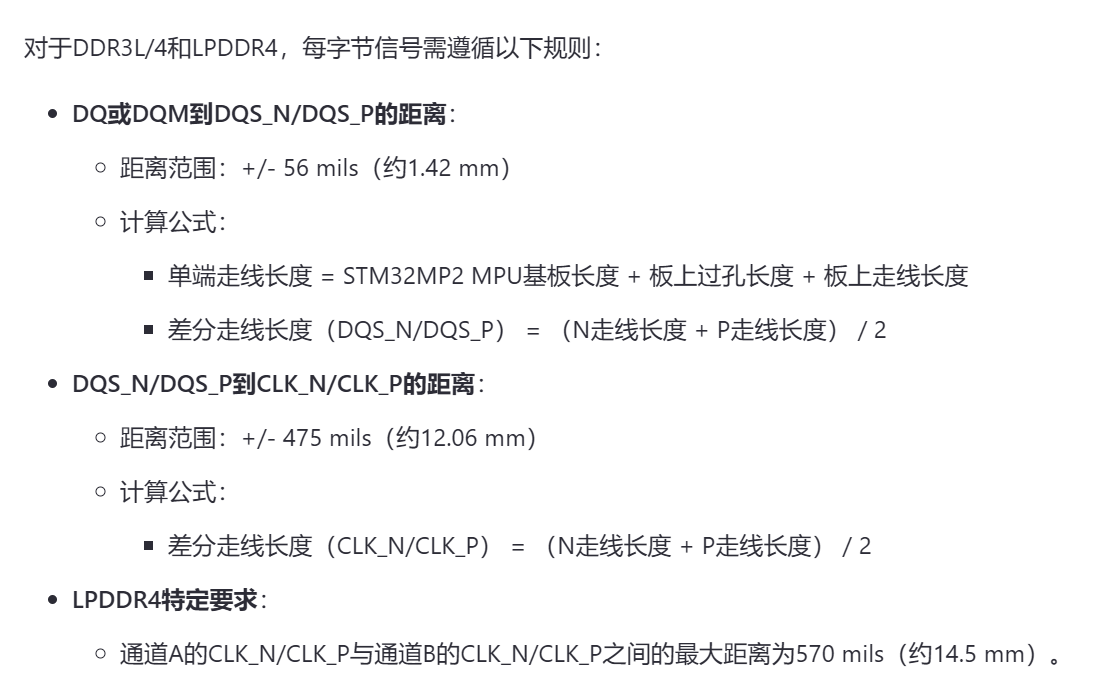

再说了走线规则

应该是间距规则,前期先随便走,走通后在 单独LAYOUT

关于数据掩码

每一组内都有一个掩码位

解释如下(感觉像是锁存)

在内存接口中,数据掩码(Data Mask,简称DQM) 是一种控制信号,用于指示在特定时钟周期内哪些数据位应被写入或忽略。具体来说,DQM信号允许在写操作期间选择性地屏蔽(即不写入)某些数据位。

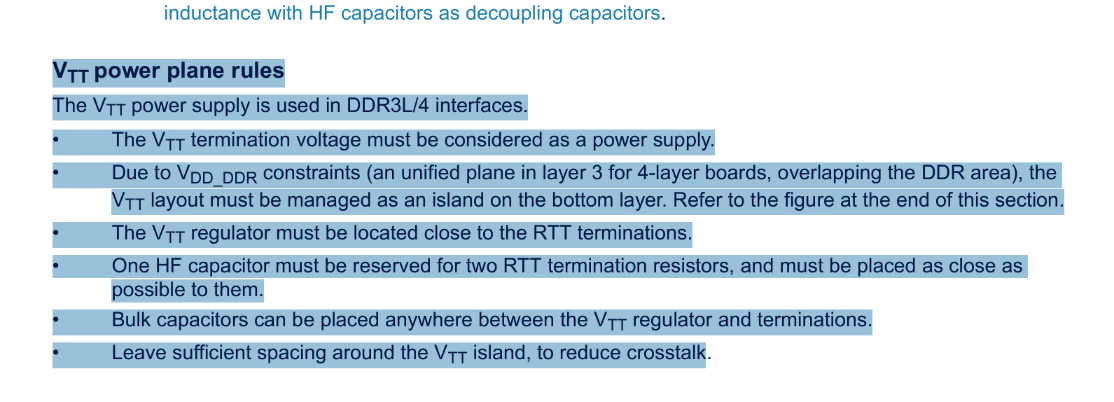

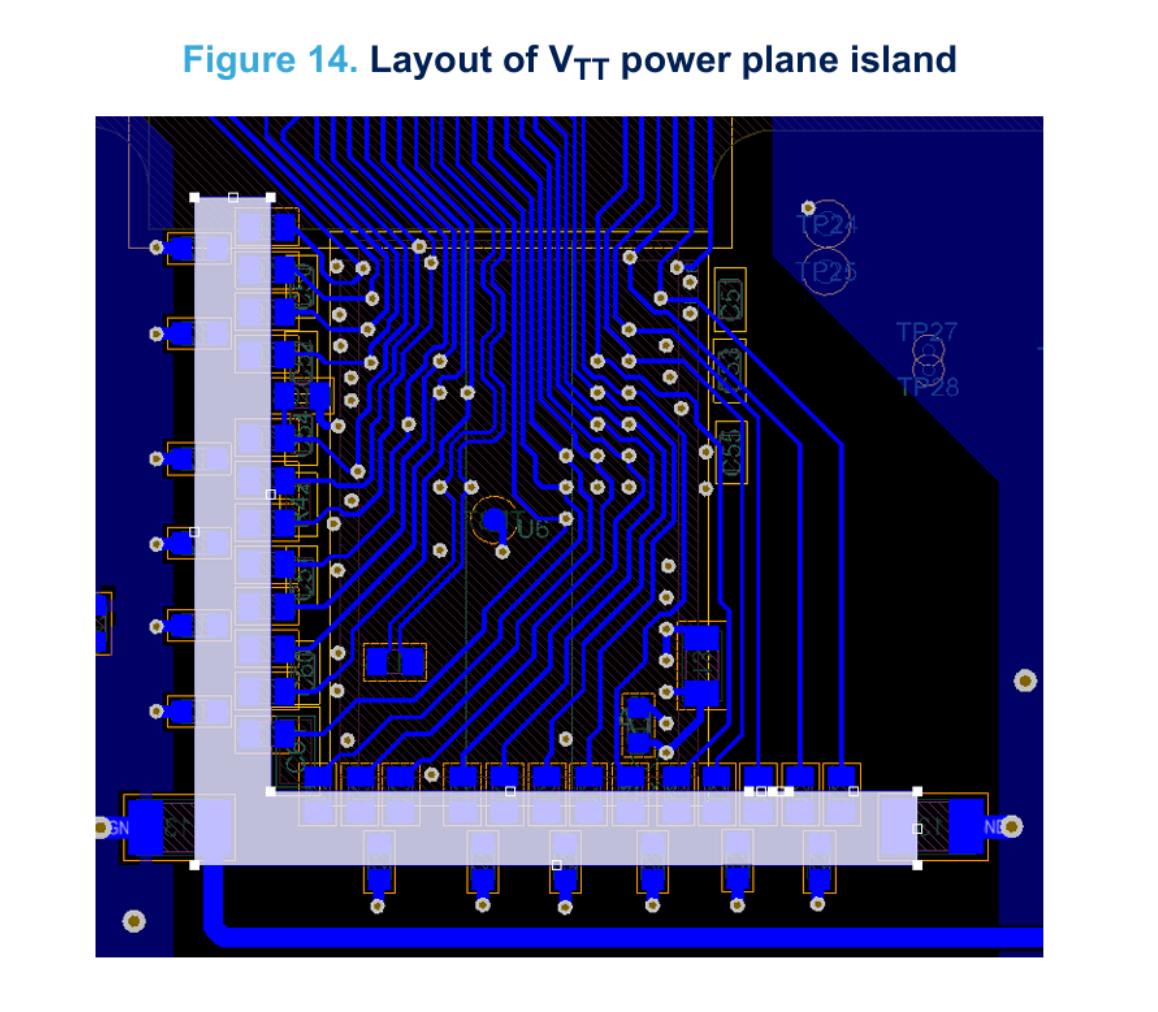

VTT终端电源的LayOUT实例

什么是VTT 电源:

VTT是用于DDR3L/4接口中的终端电阻(RTT)供电的电源 ,独立,用于保证稳定性和完整性

VTT调节器

VTT 调节器是 电源管理器件

VVT的 电阻 Rt 靠近VTT调节器 ,提高响应速度

每两个RTT终端电阻配一个HF电容

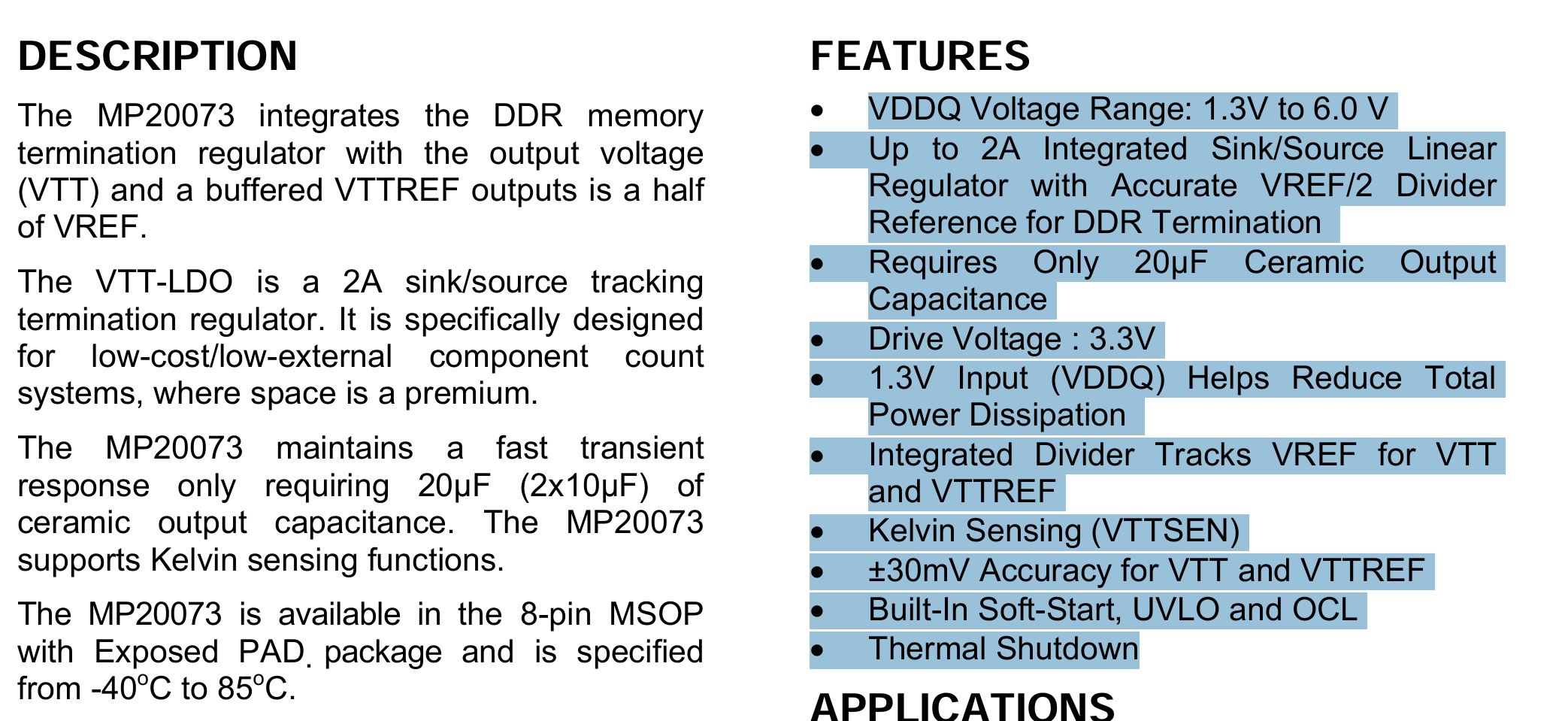

芯片实例

关于DDR的供电

对于DDR3

- VDDQ:I/O电路的供电电压,

- VTT:终端电阻的供电电压,匹配传输线的阻抗,减少信号反射

- VREF:参考电压,输入信号的电平判断,确保信号的正确识别。

- VPP:在某些特殊应用中有用,但在标准DDR3中不常见。

- VDD:内存芯片核心电路的供电电压,各模块工作电压。

AI解释==========================================================================

1. VDDQ(Supply Voltage for I/O) 也是 定义内存条 通俗说的电压

- 功能

:VDDQ是提供给DDR3内存模块输入/输出(I/O)电路的供电电压。

- 典型值

:对于DDR3,VDDQ通常为1.5V。

:

2. VTT(Termination Voltage)

- 功能

:VTT是终端电阻(RTT)的供电电压,用于匹配传输线的阻抗,减少信号反射,提高信号完整性。

- 典型值

:VTT等于VDDQ的一半(即VDDQ/2)。对于DDR3,VTT通常是0.75V(因为VDDQ是1.5V)。

- 作用

:

3. VREF(Reference Voltage)

- 功能

:VREF是参考电压,用于比较输入信号的电平,决定信号的逻辑状态(高或低)。

- 典型值

:VREF通常是VDDQ的一半(即VDDQ/2),对于DDR3,VREF是0.75V。

- 作用

:

4. VPP(Programming and Pumping Voltage)

- 功能

:VPP主要用于某些特殊应用中的编程和泵压操作,但在标准的DDR3内存接口中并不常见。

- 典型值

:在某些其他类型的存储器或特定应用场景中,VPP可能有不同的值,但在DDR3中通常不需要这个电压。

- 作用

:

5. VDD(Core Voltage)

- 功能

:VDD是提供给DDR3内存模块内部核心电路的供电电压。

- 典型值

:对于DDR3,VDD通常为1.5V。

- 作用

:

========================================================================

举例DDR电源分配

为了更好地理解这些电压的作用,以下是一些具体的应用示例:

示例1:DDR3内存模块的电源分配

假设你有一个典型的DDR3内存模块,以下是其电源分配情况:

- VDDQ = 1.5V:提供给I/O电路的供电电压。

- VTT = 0.75V:提供给终端电阻的供电电压。

- VREF = 0.75V:参考电压,用于输入信号的电平判断。

- VDD = 1.5V:提供给内存芯片核心电路的供电电压。

示例2:VTT调节器的应用

在一个DDR3内存控制器的设计中,你需要为终端电阻提供稳定的VTT电压:

- VTT调节器:选择一个能够将输入电压转换为0.75V的VTT调节器,并将其放置在尽可能靠近RTT终端电阻的位置。

- 高频去耦电容:每个高频电容服务两个RTT终端电阻,并尽可能靠近终端电阻放置,以提供局部能量储备。

- 大容量电容:根据实际布局需求,在VTT调节器和终端电阻之间选择合适的位置放置大容量电容,提供稳定的低频电源供应。

示例3:VREF的应用

在一个DDR3内存控制器的设计中,你需要为输入缓冲器提供参考电压VREF:

- VREF生成器:可以使用分压电路从VDDQ生成VREF(例如,通过两个等值电阻将1.5V分压为0.75V)。

- 滤波电容:在VREF节点添加适当的滤波电容,以减少噪声干扰,确保参考电压的稳定性。

#高速PCB设计# #DDR3# #DIY设计#

#高速PCB设计#

#高速PCB设计#

#DDR3#

#DDR3#

#DIY设计#

#DIY设计#

互动量:3306

互动量:3306

登录 或 注册 后才可以进行评论哦!

还没有评论,抢个沙发!