最开始学习linux应用开发编写的时候,估计大部分伙伴们都是在一个目录里面编译整个工程,主要是linux通常没有非常合适的集成开发环境。

以前单目录的方式实在太过捡漏,在linux环境中进行C代码工程开发很多时候需要编写一个相对比较通用的makefile,一劳永逸,能自动查找并归类每个目录的文件进行编译。

可能很多朋友会选择一些cmake,scons等自动化构建工具,但也有部分伙计编写makefile也完全够用,嵌入式平台迭代速度不快的话基本上可以成为传承级代码,那么今天大致梳理了一下makefile中构建大型一点的工程需要用到的一些编译语法与函数。

1、常用的特殊变量

这些符号是Makefile中的特殊变量,用于在规则中引用文件名和目标,

$^用于表示所有的依赖文件列表,多个文件以空格分隔。在规则中,它可以用来引用所有依赖文件的列表。例如:

target: dependency1 dependency2 dependency3 command $^

在这个例子中,$^ 将会展开为 dependency1 dependency2 dependency3。

$@/codespanstyle="color: rgb(123, 12, 0); font-size: 16px;"> 用于表示目标文件的名称。在规则中,它可以用来引用目标文件的名称。例如:

target: dependency1 dependency2 dependency3 command $@

在这个例子中,$@ 将会展开为 target。

$<用于表示规则中的第一个依赖文件。通常在单目标多源文件的情况下使用。例如:

target: dependency1 dependency2 command $<

在这个例子中,$< 将会展开为 dependency1。

$? 用于表示所有比目标文件新的依赖文件列表。通常在需要重新生成目标文件的情况下使用。例如:

target: dependency1 dependency2 command $?

在这个例子中,如果 dependency1 比 dependency2 新,则 $? 将会展开为 dependency1;如果 dependency2 比 dependency1 新,则 $? 将会展开为 dependency2;如果两者都是相同的时间戳,则 $? 将为空。

$* 用于表示规则中目标文件的文件名部分(不包括扩展名)。通常在需要将目标文件名作为参数传递给命令时使用。例如:

%.o: %.c gcc -c $< -o $@ ./process $*

在这个例子中,如果目标文件是 example.o,则 $* 将会展开为 example。

除了上面提到的 $^、$@、$<、$? 和 $*,Makefile 中还有一些其他常用的特殊变量。

$(MAKE): 用于表示 make 命令的名称。这在递归调用 make 的时候非常有用。$(CC): 用于表示 C 编译器的名称,默认情况下是 cc。你可以在 Makefile 中使用这个变量来指定编译器。$(CFLAGS): 用于表示传递给编译器的参数。这个变量通常用于指定编译选项,比如警告选项、优化选项等。$(LDFLAGS): 用于表示传递给链接器的参数。这个变量通常用于指定链接选项,比如库路径、库文件等。$(RM): 用于表示删除文件的命令,默认情况下是 rm -f。你可以在 Makefile 中使用这个变量来指定删除文件的命令。

比如$(CFLAGS) 是一个在 Makefile 中常用的特殊变量,用于指定传递给编译器的参数,可以使用它来设置编译选项,比如警告选项、优化选项等。

通常是在 Makefile 中定义 $(CFLAGS) 变量,并在编译规则中使用。例如:

CC = gcc CFLAGS = -Wall -O2 # 编译规则 %.o: %.c $(CC) $(CFLAGS) -c $< -o $@ # 默认目标all: program# 目标程序 program: file1.o file2.o $(CC) $(CFLAGS) $^ -o $@ # 清理规则 clean: rm -f *.o program

在这个示例中,$(CFLAGS) 被设置为 -Wall -O2,表示编译器应该使用所有警告选项并进行优化。然后,在编译规则中,$(CFLAGS) 被用于传递给编译器。

这样做的好处是,如果你需要修改编译选项,只需修改 $(CFLAGS) 的值,而不必在每个编译规则中都修改。这样可以使得 Makefile 更加易于维护和管理。

包括前面的特殊变量都是可以使得Makefile更加灵活和易于维护,在规则中引用文件名和目标名,而不必重复键入。

2、$(wildcard pattern)

这个规则函数看起来比较唬人,wildcard pattern英文名字就是"wildcard" 这个单词的字面意思是"通配符",那么整体就是表示为通配符表示的文件名模式,

示例:

SRCS := $(wildcard *.c)

在这个例子中,$(wildcard *.c) 将匹配当前目录下所有以 .c 结尾的文件,并将符合条件的文件名列表赋值给变量 SRCS。

另一个示例:

FILES := $(wildcard src/*.c include/*.h)

这个示例相信是很多编写C程序的makefile中经常用到的,$(wildcard src/.c include/.h) 将匹配 src 目录下的所有 .c 文件和 include 目录下的所有 .h 文件,并将结果合并为一个文件列表赋值给变量 FILES。

3、$(patsubst pattern,replacement,text)

在 Makefile 中,$(patsubst pattern,replacement,text) 是一个用于模式替换的函数,将文本中符合指定模式的部分替换为指定的字符串。

这个函数通常用于对文件名或路径进行模式匹配和替换,非常适合在 Makefile 中进行文件名的转换操作。

$(patsubst pattern,replacement,text) 参数: pattern:要匹配的模式,可以包含通配符 * 和 ?。 replacement:要替换成的字符串。 text:要进行模式替换的文本。

比如如下这个简单的例子:

SOURCES := file1.c file2.c file3.c OBJECTS := $(patsubst %.c,%.o,$(SOURCES))

将会把 SOURCES 变量中以 .c 结尾的文件名替换为以 .o 结尾的文件名,最终将得到 OBJECTS 变量的赋值结果为 “file1.o file2.o file3.o”。

4、addprefix

Makefile 中,$(addprefix prefix,names…) 是一个函数,用于将指定的前缀添加到一组空格分隔的文件名中。

这个函数通常用于将相同的前缀添加到一组文件名或路径中,非常适合在 Makefile 中进行路径拼接操作。

语法:

$(addprefix prefix,names...) 参数: prefix:要添加的前缀。 names…:一组空格分隔的文件名或路径。

示例:

SOURCES := file1.c file2.c file3.c OBJS := $(addprefix obj/,$(SOURCES:.c=.o))

在这个例子将会在 SOURCES 变量中的每个文件名后面添加 obj/ 前缀,并将处理后的结果赋值给 OBJS 变量。最终得到的 OBJS 变量的值为 “obj/file1.o obj/file2.o obj/file3.o”。

5、notdir

$(notdir names…) 是一个函数,用于获取一组文件名或路径中的文件名部分,并将其返回。

这个函数通常用于从给定的路径中提取文件名部分,非常适合在 Makefile 中进行文件处理操作。

语法:

$(notdir names...) 参数: names…:一组空格分隔的文件名或路径。

示例:

SRCS := src/file1.c src/file2.c src/file3.c OBJS := $(notdir $(SRCS))

$(notdir $(SRCS)) 将会从 SRCS 变量中的每个文件路径中提取文件名部分,并将处理后的结果赋值给 OBJS 变量,最终得到的 OBJS 变量的值为 “file1.c file2.c file3.c”。

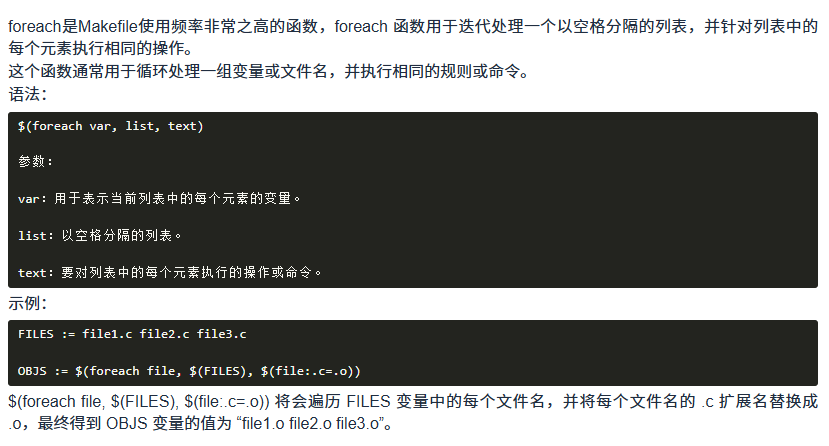

6、foreach

7、最后总结

好了,基本上使用上介绍这些函数能够解决大部分的文件查找和文件名替换工作,最终就是编译了,对于C的编译过程无非就是编译、链接、清除,就是不细说了。

其实makefile主要就是自动化构建,把我们的源文件、库文件加工处理,那么只要我们的源文件位置没有大变动、编译过程无特别的要求,那么通用化makefile模板做好以后,后续就只需要进行源文件位置的添加和编译选项额修改,跟用那么集成开发环境添加一个一个的路径是一样的。

# 默认目标all: program#

# 默认目标all: program#

互动量:1312

互动量:1312

登录 或 注册 后才可以进行评论哦!