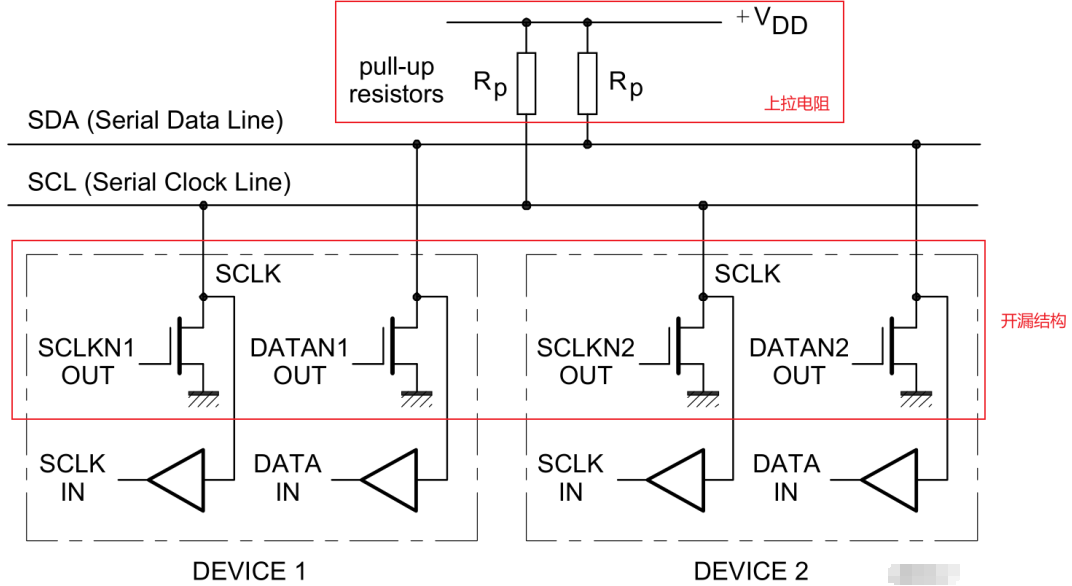

I2C为什么要用上拉电阻?

因为I2C是开漏结构输出,高电平靠外部上拉,假如有一个 GPIO 接地,那么电流会通过上拉电阻流进地,因为有上拉电阻的存在,所以电流不大,不会损坏 GPIO 口。

上拉电阻过小,电流大,端口低电平 level 增大,会发现总线上电平拉不到 0V。

上拉电阻过大,上升沿时间增大,方波可能会变成三角波。

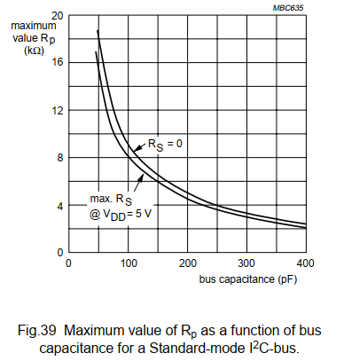

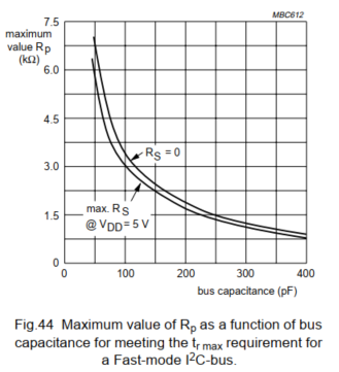

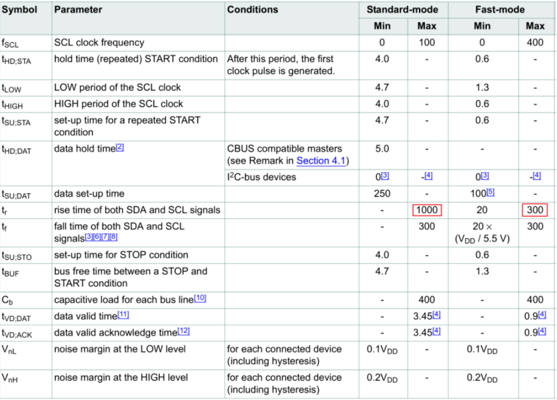

最大电阻和上升沿时间 tr 、总线电容 Cb 、标准上升沿时间有关。

最小电阻和电源 VDD 电压、GPIO 最大输出电压 VOL、 GPIO 最大电流IOL 有关。

计算方法:

(1)用Rp(max)和Cb函数关系图求上拉电阻Rp(max)

太复杂?我也这么觉得,有简便方法吗?

(2)用电容充电公式求上拉电阻Rp(max)

下面我们计算一下上升时间tr:

已知输入电平阈值与VDD相关:VIH = 0.7VDD,VIL = 0.3VDD。

根据电容充电公式可以得到:

V(t) =VDD (1−e−t/RC)

其中:t是充电时间,RC是时间常数。

电容充到0.3VDD的时间:V(t1)= 0.3×VDD = VDD (1−e−t1/RC),

t1 = 0.3566749×RC;

电容充到0.7VDD的时间:V(t2)= 0.7×VDD = VDD (1−e−t2/RC),

t2 = 1.2039729×RC;

上升沿时间:tr = t2-t1 = 0.8473×RC。

可推出上拉电阻的公式:

Rp(max)=tr/(0.8473×Cb)

标准模式 :

Rp(max)=tr/(0.8473×Cb)=1000×10−9/0.8473×200×10−12=5.9KΩ

快速模式:

Rp(max)=tr/(0.8473×Cb)=300×10−9/0.8473×200×10−12=1.77KΩ

高速模式虽说也有上拉电阻,但其主机内部集成了恒流源,可以加快tr(上升沿时间 ),所以对上拉电阻不做特殊规定。

一般在不同速率采用的电阻分别为:4.7K、2.2K、1.5K。

从上图可以得到最大电阻和最小电阻计算公式以及如下数据:

1、标准模式:0~100KHz,上升沿时间要求 tr = 1us

2、快速模式:100~400KHz,上升沿时间要求 tr = 0.3us

note:该上升沿时间 tr 是 0.3VDD到 0.7VDD 的时间要求。

互动量:1171

互动量:1171

登录 或 注册 后才可以进行评论哦!